# FEATURES AND BENEFITS

- Sensorless (no Hall sensors required)

- Closed loop speed control

- Minimal external components

- PWM speed input

- FG speed output

- Lock detection

- Soft start

- Overcurrent protection

- Soft switching for reduced audible noise

## Package: 20-contact QFN (suffix ES)

# DESCRIPTION

The A4942 three phase motor driver incorporates BEMF sensing to eliminate the requirement for Hall sensors in fan applications.

A closed loop speed control system is integrated into the IC. This allows accurate setting of maximum and minimum speeds via selection of external resistors. The speed is controlled by duty cycle demand applied to the PWM input. The PWM input is allowed to operate over a wide frequency range.

Current limiting is integrated to allow saving the cost and PCB space of an external sense resistor. The current limit function includes an adjustable soft start to minimize load on the power supply while the fan is ramping up to speed.

The A4942 is supplied in a 20-contact 4 mm × 4 mm QFN package (suffix ES) with exposed pad for enhanced thermal dissipation. The package is lead (Pb) free, with 100% matte tin leadframe plating.

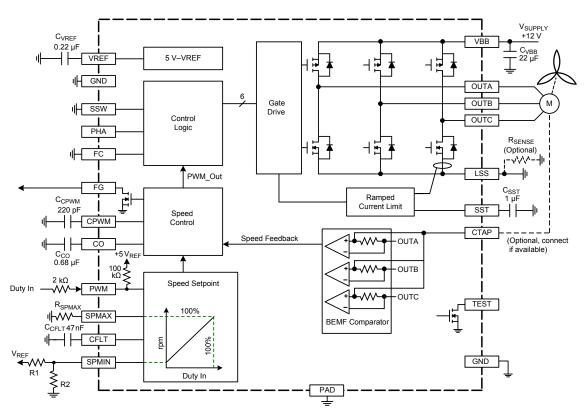

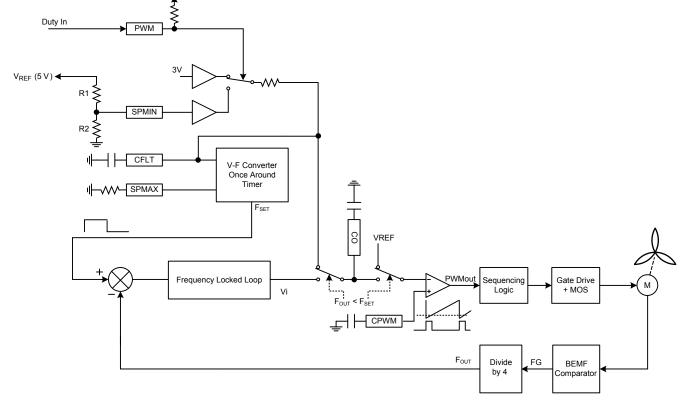

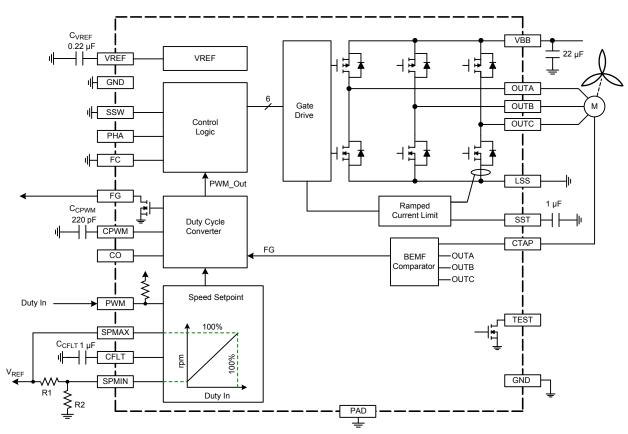

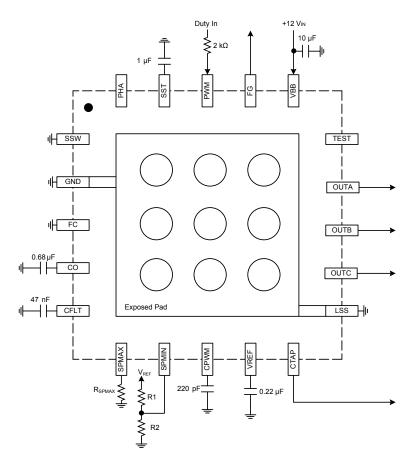

Functional Block Diagram

## SPECIFICATIONS

#### **SELECTION GUIDE**

| Part Number  | Packing                    | Package                                 |

|--------------|----------------------------|-----------------------------------------|

| A4942GESTR-T | 1500 pieces per 7-in. reel | 20-contact QFN with exposed thermal pad |

### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                | Symbol               | Notes                                      | Rating          | Unit |

|-------------------------------|----------------------|--------------------------------------------|-----------------|------|

| Supply Voltage                | V <sub>BB</sub>      |                                            | 16              | V    |

| Logic Input Voltage Range     | V <sub>IN</sub>      | PWM                                        | –0.3 to 6       | V    |

| Logic Output                  | Vo                   | FG                                         | V <sub>BB</sub> | V    |

| Outrast Comment               |                      | Locked rotor condition, internally limited | 1.6             | A    |

| Output Current                | IOUT                 | Duty Cycle = 100%                          | 800             | mA   |

| Operating Ambient Temperature | T <sub>A</sub>       | G temperature range                        | -40 to 105      | °C   |

| Maximum Junction Temperature  | T <sub>J</sub> (max) |                                            | 150             | °C   |

| Storage Temperature           | T <sub>stg</sub>     |                                            | –55 to 150      | °C   |

### THERMAL CHARACTERISTICS: May require derating at maximum conditions: see application information

| Characteristic              | Symbol                | Test Conditions                              | Value | Unit |

|-----------------------------|-----------------------|----------------------------------------------|-------|------|

| Deskens Themsel Desister of | $R_{	extsf{	heta}JA}$ | 2-sided PCB with 0.60 in <sup>2</sup> copper | 75    | °C/W |

| ackage Thermal Resistance   |                       | 4-layer PCB based on JEDEC standard          | 37    | °C/W |

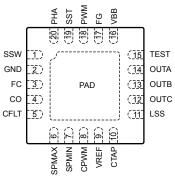

## **PINOUT DIAGRAM AND TERMINAL LIST**

**Pin-out Diagram**

|--|

| Number                          | Name  | Function                                  |

|---------------------------------|-------|-------------------------------------------|

| 1                               | SSW   | Soft switch duty cycle adjust             |

| 2                               | GND   | Ground                                    |

| 3                               | FC    | Capacitor to set startup oscillator       |

| 4                               | CO    | Speed control loop comparator capacitor   |

| 5                               | CFLT  | PWM filter capacitor                      |

| 6                               | SPMAX | Speed curve set maximum                   |

| 7 SPMIN Speed curve set minimum |       | Speed curve set minimum                   |

| 8                               | CPWM  | Set motor PWM frequency                   |

| 9                               | VREF  | Reference voltage output                  |

| 10                              | CTAP  | Motor terminal center tap                 |

| 11                              | LSS   | Ground                                    |

| 12                              | OUTC  | Motor terminal phase C                    |

| 13                              | OUTB  | Motor terminal phase B                    |

| 14                              | OUTA  | Motor terminal phase A                    |

| 15                              | TEST  | Test use only – open circuit              |

| 16                              | VBB   | Input supply                              |

| 17                              | FG    | Speed output signal                       |

| 18                              | PWM   | Logic input – speed (demand 1 to 100 kHz) |

| 19                              | SST   | Soft start adjustable current limit       |

| 20                              | PHA   | Logic input – 3 state select              |

| _                               | PAD   | Exposed thermal pad                       |

| Characteristic                                  | Symbol                             | Test Conditions                                                           | Min. | Тур. | Max. | Unit |

|-------------------------------------------------|------------------------------------|---------------------------------------------------------------------------|------|------|------|------|

| VBB Voltage Range                               | V <sub>BB</sub>                    |                                                                           | 5    | -    | 16   | V    |

| VBB Supply Current                              | I <sub>BB</sub>                    |                                                                           | _    | 13.5 | 15   | mA   |

| Total Driver On-Resistance<br>(Sink + Source)   | R <sub>DS(on)</sub>                | I <sub>OUTx</sub> = 800 mA, T <sub>J</sub> = 25°C, V <sub>BB</sub> = 12 V | -    | 1    | 1.2  | Ω    |

|                                                 |                                    | LSS = GND, $T_J = 25^{\circ}C$                                            | 1.3  | 1.45 | 1.6  | А    |

| Overcurrent Threshold                           | I <sub>CL</sub>                    | LSS = GND, $T_J = -40^{\circ}$ C to $105^{\circ}$ C                       | 1.1  | -    | 1.8  | А    |

| Overcurrent Threshold Voltage                   | V <sub>OCL</sub>                   |                                                                           | 185  | 200  | 215  | mV   |

| PWM Low Level                                   | V <sub>IL</sub>                    |                                                                           | 0    | -    | 1    | V    |

| PWM High Level                                  | V <sub>IH</sub>                    |                                                                           | 2    | -    | 5.5  | V    |

| Input Hysteresis                                | V <sub>HYS</sub>                   |                                                                           | -    | 300  | _    | mV   |

| Logic Input Current                             | I <sub>IN</sub>                    | PWM pin, V <sub>IN</sub> = 0 V                                            | -    | -50  | _    | μA   |

| Output Saturation Voltage<br>(FG and TEST pins) | V <sub>SAT</sub>                   | I <sub>FG</sub> = 5 mA                                                    | -    | _    | 0.3  | V    |

| FG Output Leakage                               | I <sub>FG</sub>                    | V <sub>FG</sub> = 16 V                                                    | -    | -    | 1    | μA   |

| Lock Protection                                 | t <sub>ON</sub>                    |                                                                           | 1.35 | 1.5  | 1.65 | s    |

|                                                 | t <sub>OFF</sub>                   |                                                                           | 9    | 10   | 11   | s    |

| Lock Ratio                                      | t <sub>OFF</sub> / t <sub>ON</sub> |                                                                           | 6.33 | 6.67 | 7    | _    |

| Startup Oscillation Time                        | t <sub>FC</sub>                    | Relative to target, C = 47 nF                                             | -20  | -    | 20   | %    |

| Soft Start Time                                 | t <sub>SST</sub>                   | Relative to target, C = 1 $\mu$ F                                         | -20  | -    | 20   | %    |

| VBB Pin Undervoltage Lockout<br>(UVLO)          | V <sub>BBUVLO</sub>                | V <sub>BB</sub> rising                                                    | 4.5  | 4.75 | 4.95 | V    |

| VBB Pin UVLO Hysteresis                         | VBBUVLOHYS                         |                                                                           | 100  | 200  | 300  | mV   |

| Speed Saturaint                                 | £                                  | R <sub>SPMAX</sub> = 20 kΩ, PWMOUT = 20% to 100%                          | -5   | -    | 5    | %    |

| Speed Setpoint                                  | f <sub>SET</sub>                   | R <sub>SPMAX</sub> = 20 kΩ, PWMOUT = 10% to 20%                           | -10  | -    | 10   | %    |

| Internal PWM Frequency                          | f <sub>PWM</sub>                   | C <sub>CPWM</sub> = 220 pF                                                | 55   | 64   | 73   | kHz  |

| VREF Output Voltage                             | V <sub>REF</sub>                   | $I_{VREF}$ = 0 to 5 mA, $V_{BB}$ = 12 V                                   | 4.8  | 5    | 5.2  | V    |

| Thermal Shutdown Temperature                    | T <sub>JTSD</sub>                  | Temperature increasing                                                    | 150  | 165  | 180  | °C   |

| Thermal Shutdown Hysteresis                     | T <sub>JHYS</sub>                  | Recovery = T <sub>JTSD</sub> – T <sub>JHYS</sub>                          | _    | 20   | _    | °C   |

NOTE 1: Specified limits are tested at a single temperature and assured across the operating temperature range by design and characterization.

### FUNCTIONAL DESCRIPTION

**Lock Detect** Valid commutation signals must be detected to ensure the motor is not stalled. If a valid FG signal is not detected for 1.5 s, the outputs will be disabled for 10 s before an autorestart is attempted.

**VREF** Reference voltage output used to bias external resistor dividers. External current draw should be no more than 5 mA.  $V_{REF}$  supply must be decoupled with a 0.22 µF ceramic capacitor.

**FG** Open drain output that provides speed information to the system.

**Current Limit** During a locked rotor condition, the current will ramp up to the internal current limit. Load current is monitored on the low-side MOSFET. If the current reaches the Overcurrent Threshold,  $I_{CL}$ , the drivers will be chopped at a frequency set by  $C_{PWM}$ .

Optionally, current limit can be set as:

Current Limit =

$$200 \text{ mV} / R_{SENSE}$$

where R<sub>SENSE</sub> is an optional external component on the LSS pin.

If it is preferable to save expense and the PCB space of an external component, connect LSS to GND. This sets the current limit to the internal threshold of 1.45 A typical. Using an external resistor can only lower the current limit below the internal threshold.

**PWM Input** The PWM pin is the speed command input. The input frequency can be in the range from 1 to 100 kHz.

If PWM is left open circuit, the motor will run at maximum demand.

**CPWM** The internal PWM frequency,  $f_{PWM}$ , is selected via an external capacitor on the CPWM pin. The recommended range is 20 to 80 kHz, calculated as:

$$f_{PWM} = 1.41 \times 10^{-5} / C_{PWM}$$

**CTAP** Connection pin for motor center-tap if available. If not available (such as with delta type motors), the null point will be generated internally.

**CFLT** Terminal for an external capacitor to filter PWM input, set based on PWM input frequency.  $C_{FLT}$  has a typical value of 47 nF for a 56 kHz signal input at the PWM pin.

**Soft Start** The soft start function is controlled by an external capacitor on the SST pin. Typically the motor speed will limit the current, as BEMF builds up before the current limit is reached. The current limit is ramped in a linear fashion, from close to zero amperes to the current limit value.  $C_{SST}$  should be in the range from 100 nF to 2.2  $\mu$ F, and the resulting soft start period can be calculated as:

$$T_{SST} = 5 \times 10^6 \times C_{SST}$$

**FC** Analog input terminal for external capacitor to set startup commutation time:

$$T_{FC} = 1 \times 10^6 \times C_{FC}$$

For FC connected to GND, t<sub>FC</sub> is 50 ms.

**PHA** Phase Advance input, sets the internal lead angle according to the external connection as follows:

#### Table 1: PHA Pin Connections

| PHA Pin Connection | Electrical Degrees |

|--------------------|--------------------|

| GND                | 24                 |

| VREF               | 6                  |

| Open               | 15                 |

Lead angle adjustment advances the applied voltage relative to rotor position.

**TEST** Open drain output for test use only.

# A4942

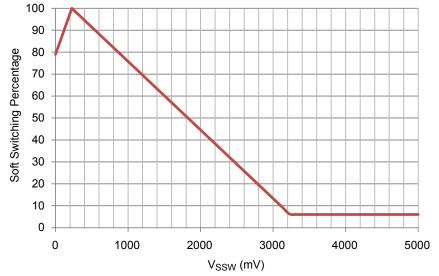

**Soft Switch** A resistor divider from VREF to GND sets the soft switching characteristic. The voltage at the SSW pin sets the range of soft switching, as shown in Figure 1.

**R**<sub>SPMAX</sub> Connect external resistor to GND to set motor speed at 100% demand. Select the resistor value as:

Maximum Speed (rpm) =

$$\frac{4 \times 10^8}{R_{\text{SPMAX}}}$$

By connecting SSW to GND the nominal Soft Switching value of 78% can be used, while saving external component cost and PCB space. Note: Soft switching should be tested in the application at maximum open loop speed. If the motor stalls, decrease the % Soft Switching value.

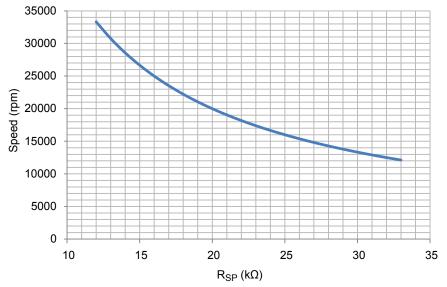

where he relationship of speed to  $R_{SPMAX}$  is shown in Figure 2.

Figure 1: Soft Switching Percentage as a Function of Voltage on SSW Pin

Figure 2: Commutation Speed as a Function of Resistor Value on SPMAX Pin

## **APPLICATION INFORMATION**

### **Closed Loop Speed Control System**

The VREF, SPMIN and SPMAX pins are used to select the endpoints of the linear speed curve characteristic (4-pole motor).

Referring to Figure 3, at startup, speed demand is controlled by  $\ensuremath{V_{\text{REF}}}\xspace.$

Given that:

### Maximum Speed (rpm) = $4 \times 10^8$ / $R_{SPMAX}$

then:

Minimum Speed (rpm) = Maximum Speed (rpm)  $\times$  (5/3)

$$\times R_2 / (R_1 + R_2)$$

$R_1 + R_2$  should be set close to 25 k $\Omega$ .

At start-up speed demand is connected to VREF. As soon as speed exceeds the target speed, the speed demand control switches to the output of the frequency locked loop. The  $C_{CO}$  value, an external capacitor on the CO pin, sets the bandwidth of speed control loop.  $C_{CO}$  is charged or discharged based on the comparison of the falling edge of  $f_{OUT}$  and  $f_{SET}$ . The typical value is 0.68  $\mu$ F.

Figure 3: Equivalent Circuit of Closed Loop Control System

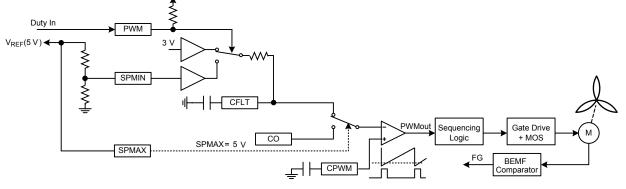

## **Open Loop Speed Control System**

An alternative, open loop control system can be applied, as shown in figure 4.

The closed loop speed control system can be disabled by connecting SPMAX to VREF. In this case,  $V_{CFLT}$  will be compared to the  $C_{PWM}$  sawtooth waveform to create the PWM output duty

applied to the motor. (The  $C_{CO}$  capacitor is not required.) This configuration is shown in figure 5.

Larger  $C_{FLT}$  capacitor values can be used to slow down response in the case of large duty changes expected at the PWM input.

Figure 4: Equivalent Circuit of Open Loop Control System

Figure 5: Functional Block Diagram Demonstrating Implementation of Open Loop Control

## **Layout Notes**

A typical layout is illustrated in figures 6 and 7. Recommended component values for this layout are provided in the table.

The following guidelines for PCB layout should be observed:

- Place  $C_{\text{VREF}}$  and  $C_{\text{CPWM}}$  as close as possible to the IC

- Route high impedance signal traces (CO, CFLT, and SST) away from switching nodes (OUTA, OUTB, OUTC, and CTAP)

- Connect GND and LSS directly to the exposed pad under the IC

- Utilize the ground plane on the bottom side of the PCB under the IC for low impedance returns to  $\rm C_{VBB}$  and the power connector

| Symbol                            | Value                  | Note                                        |  |  |  |

|-----------------------------------|------------------------|---------------------------------------------|--|--|--|

| C <sub>FC</sub>                   | Connect to GND         | Only required if start-up<br>problems found |  |  |  |

| C <sub>CFLT</sub>                 | 47 nF X5R / 6.3 V      |                                             |  |  |  |

| C <sub>CO</sub>                   | 0.68 µF X5R / 6.3 V    | 0.68 $\mu$ F is the minimum value           |  |  |  |

| C <sub>CPWM</sub>                 | 220 pF X5R / 6.3 V     | Sets motor PWM to 64 kHz                    |  |  |  |

| C <sub>SST</sub>                  | 1 µF X5R / 6.3 V       |                                             |  |  |  |

| C <sub>VBB</sub>                  | 10 to 22 µF X5R / 25 V |                                             |  |  |  |

| C <sub>VREF</sub>                 | 0.22 µF X5R /10 V      |                                             |  |  |  |

| R <sub>SPMAX</sub>                | 10 to 50 kΩ, 1%        | Select for design maximum speed             |  |  |  |

| R <sub>SPMIN</sub><br>(R1 and R2) | 1%                     | R1 plus R2 close to 25 k $\Omega$ total     |  |  |  |

### **Table 2: Recommended External Components**

Figure 6: Typical PCB Layout

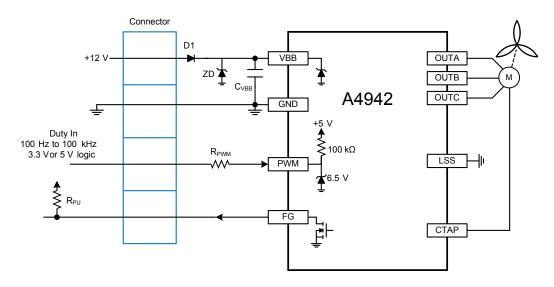

## Fan System

A typical integrating into a fan system is shown in figure 7.

Optional External Components

Typically a 4-pin connector is used to interface the system to a fan module and the A4942.

- It may be a requirement in the end application to ensure these pins survive reverse polarity connection or incorrect application of signals during the fan test process.

- D1 can be added to handle the requirement or reverse polarity connection. D1 should be a low  $V_f$ , 2 A/20 V rated component. Adding D1 will reduce efficiency and maximum speed due to the voltage drop and power loss.

- If D1 is used, then typically a clamp diode (ZD) is required to prevent voltage transients from exceeding the maximum rating to the IC. When the fan is turned off, due to the inductance

of the load, the current path is back into the  $\rm C_{VBB}$  capacitor, because D1 prevents flow back towards the 12 V supply capacitor.  $\rm V_{BB}$  overshoot will result until the energy in the load is dissipated.

- ZD is required to clamp below the VBB pin ESD structure breakdown (approximately 20 V). If the energy stored in inductance is low enough,  $C_{VBB}$  can be increased, to lower the overshoot to a safe level, and ZD would not be required.

- Including  $R_{PWM}$  is recommended to isolate the PWM pin from the external world. The maximum rating of the PWM pin is 6 V. However, including  $R_{PWM}$  would limit the current in case of an accidental connection to VBB. With this current limit, the PWM pin ESD diode would break down at 6.5 V. The IC would not be damaged with less than 8 mA bias into the pin. 2 k $\Omega$  is the recommended value.

Figure 7: Typical Fan System Configuration

# A4942

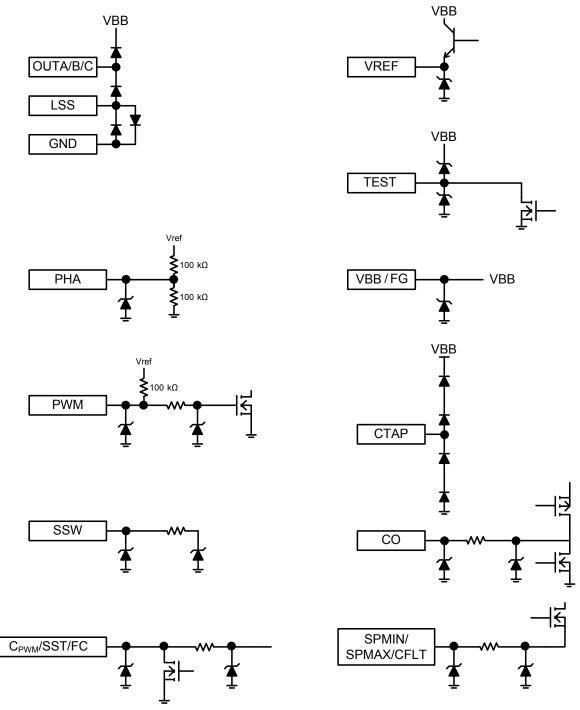

**PIN STRUCTURES**

Figure 8: Pin Structures

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

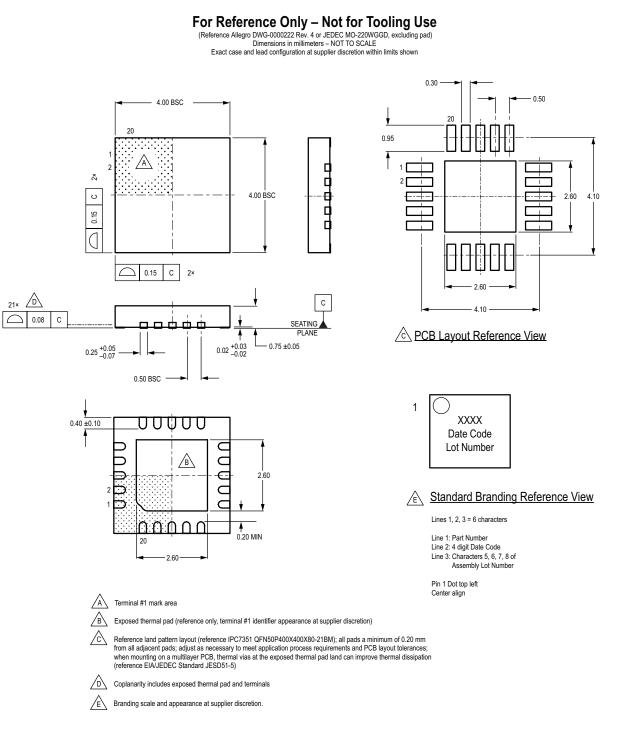

### PACKAGE OUTLINE DIAGRAM

Figure 9: Package ES, 20-Pin QFN with Exposed Thermal Pad

**Revision History**

| Number | Date          | Description                                     |

|--------|---------------|-------------------------------------------------|

| 4      | July 25, 2019 | Minor editorial updates; initial release to web |

| 5      | July 27, 2021 | Updated package drawing (page 12)               |

Copyright 2021, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com