## FEATURES AND BENEFITS

- AEC-Q100 qualified

- +  $V_{IN}$  range: 5.3 to 40 V supply, operates down to 5.1 V when enabled

- Four independent MOSFET drivers

- Internal and external PWM dimming options

Internal DWM dimming act has position division

- □ Internal PWM dimming set by resistor divider or analog voltage

- □ External PWM dimming set by microcontroller

- Flexible LED analog dimming options

- Two ADIM pins for LED binning, NTC feedback, or hybrid analog/PWM dimming

- $\hfill\square$  Adjustable integrated LED current derating for elevated  $V_{IN}$

- Integrated LED current derating for elevated IC junction temperature

- Combine A80804 devices in parallel for higher number of LED strings; PWMOUT signal available when used with internal PWM for master/slave operation

- MINOUT signal available to trim a pre-regulator to minimize power loss

- Selectable LED current slew rate limit during PWM dimming

- Extensive fault detection and protection

Drain short-to-ground detection

- □ Drain short-to-VIN

- □ Open LED

- $\Box$  Thermal protection

- □ Programmable input UVLO

# DESCRIPTION

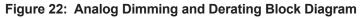

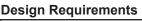

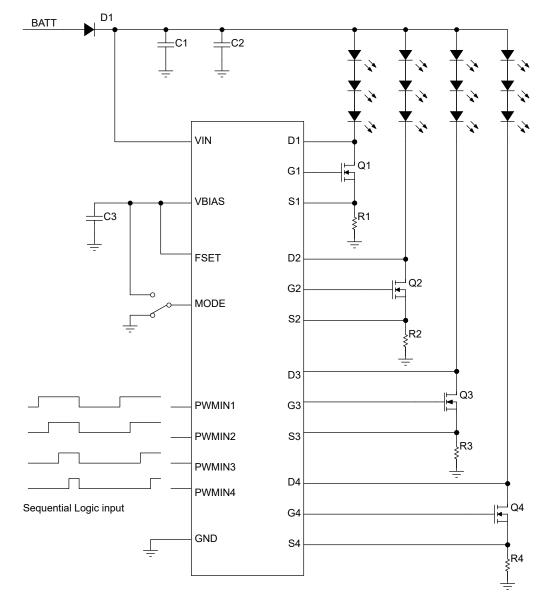

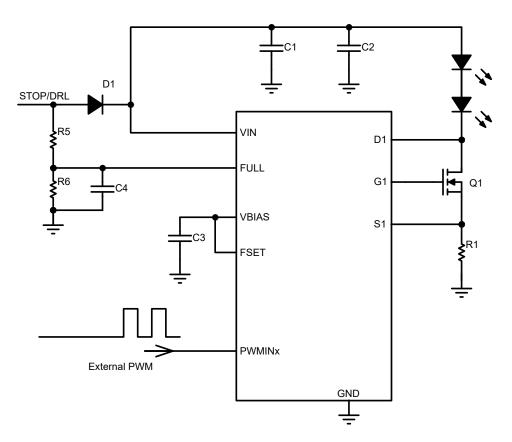

The A80804 and A80804-1 are linear, programmable current controllers capable of accurately regulating current in four LED strings using external MOSFETs. Each of the four LED drivers has an independent enable/PWM input and current-sense resistors and can be independently dimmed with an external PWM signal, or all channels can be dimmed with internal PWM dimming and automatic phase shifting. The overall LED current can be switched between low and full intensity for applications including stop/tail or DRL/position lighting. Multiple analog dimming options are available to support applications including LED binning, NTC foldback, or hybrid dimming. A selectable LED current slew-rate control is available to tune PWM edge times and improve EMI performance.

The MINOUT feature allows for trimming an external DC-DC converter to optimize the voltage across the linear current regulating MOSFETs to minimize power loss.

The A80804 offers several fault detection and protection options including MOSFET drain short-to-ground, drain short-to-VIN, open-LED fault protection, internal overtemperature protection, and undervoltage lockout. The A80804 can be configured for either one-out-all-out or one-out-continue operation.

The A80804 has a 500 mV current-sense reference for improved BCI performance. The A80804-1 has a 200 mV current-sense reference for lower power dissipation in the sense resistor.

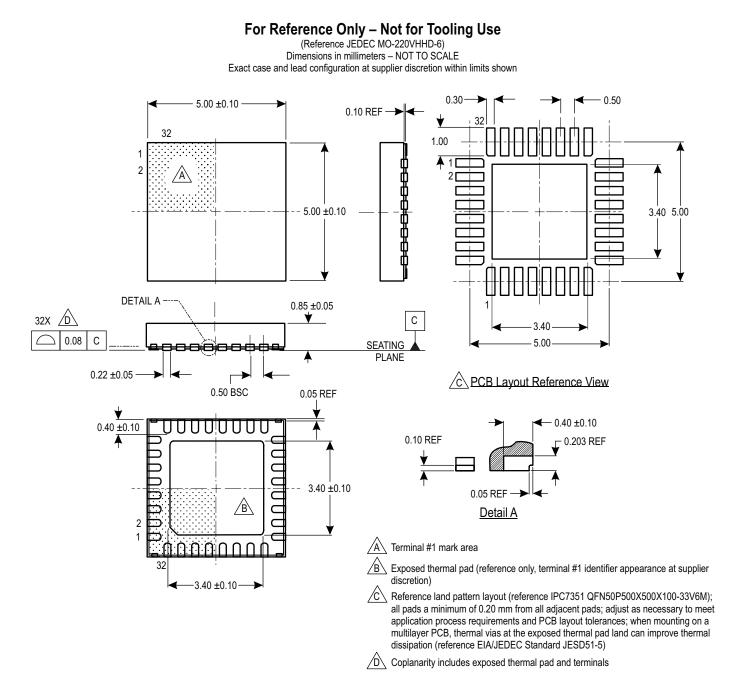

The device is packaged in a 32-pin QFN (ET) with exposed pad for enhanced thermal dissipation and wettable flank construction for solderability and visual inspection.

# **APPLICATIONS**

- Automotive medium-power LED lighting systems

- Fog lights, backup lights, daytime running lights, position lights, sequential light

## PACKAGE

32-contact QFN 5 mm × 5 mm × 0.90 mm with exposed thermal pad and wettable flank (suffix ET)

Not to scale

VIN FULL

TAIL/PSTN

STOP/D

1

#### **SELECTION GUIDE**

| Part Number    | V <sub>SENSE</sub> Option (mV) | Package                                     | Packing <sup>[1]</sup>      |

|----------------|--------------------------------|---------------------------------------------|-----------------------------|

| A80804KETASR   | 500                            | 32-pin 5 mm × 5 mm QFN                      | 1500 pieces per 7 inch real |

| A80804KETASR-1 | 200                            | with exposed thermal pad and wettable flank | 1500 pieces per 7-inch reel |

<sup>[1]</sup> Contact Allegro for additional packing options.

#### **ABSOLUTE MAXIMUM RATINGS**<sup>[2]</sup>

| Characteristic                                     | Symbol              | Notes | Rating     | Unit |

|----------------------------------------------------|---------------------|-------|------------|------|

| VIN, FULL, nFAULT, PWMINx, Dx, Gx, and MINOUT Pins |                     |       | -0.3 to 45 | V    |

| All other pins                                     |                     |       | –0.3 to 7  | V    |

| Maximum Continuous Junction Temperature            | T <sub>J(MAX)</sub> |       | 150        | °C   |

| Transient Junction Temperature                     | TJ                  |       | 175        | °C   |

| Storage Temperature Range                          | T <sub>stg</sub>    |       | –55 to 150 | °C   |

[2] Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS

| Characteristic                         | Symbol           | Test Conditions <sup>[3]</sup>         | Value | Unit |

|----------------------------------------|------------------|----------------------------------------|-------|------|

| Junction to Ambient Thermal Resistance | R <sub>θJA</sub> | On 4-layer PCB based on JEDEC standard | 30    | °C/W |

<sup>[3]</sup> Additional thermal information available on the Allegro website.

## **Table of Contents**

| Features and Benefits              |    |

|------------------------------------|----|

| Description                        |    |

| Applications                       |    |

| Package                            | 1  |

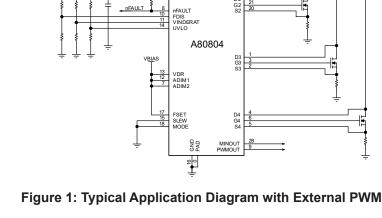

| Typical Application Diagram        | 1  |

| Selection Guide                    | 2  |

| Absolute Maximum Ratings           | 2  |

| Thermal Characteristics            | 2  |

| Terminal Diagram and Terminal List |    |

| Functional Block Diagram           | 4  |

| Electrical Characteristics         | 5  |

| Functional Description             | 8  |

| LED Current Sense Resistor         | 8  |

| LED PWM Dimming                    | 8  |

| Full Mode                          | 9  |

| Analog Dimming                     | 9  |

| LED Current Slew Control           | 10 |

| PWMOUT                             | 10 |

|                                    |    |

| MINOUT                                                    | 11        |

|-----------------------------------------------------------|-----------|

| Protection Functions                                      | 11        |

| Applications Information 2                                | 21        |

| MOSFET Selection Guidelines2                              | 21        |

| Four 2-LED Channels, Internal PWM at 200 Hz,              |           |

| 5% Duty Cycle, Without Analog Dimming2                    | 22        |

| Four 2-LED Channels, External PWM, Analog Dimming at 80%2 | 24        |

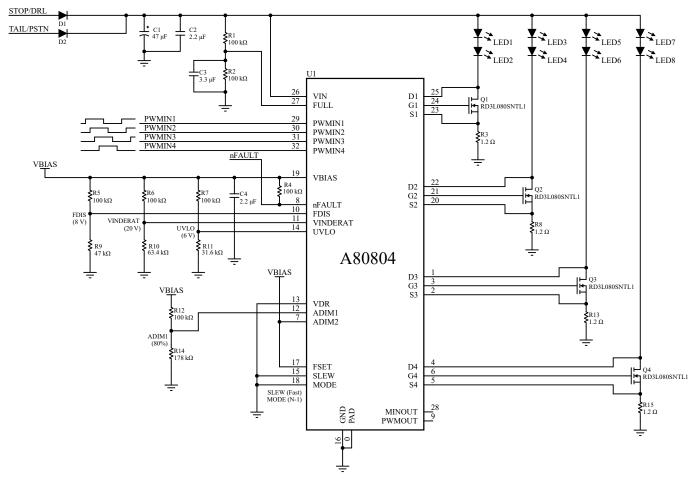

| Multiple A80804 Master-Slave Arrangement 2                | 26        |

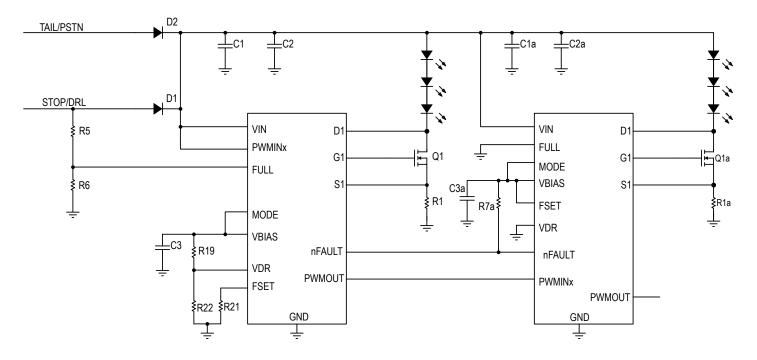

| Multiple A80804 In Parallel with External Dimming2        | 27        |

| Sequential LED Driver2                                    | 28        |

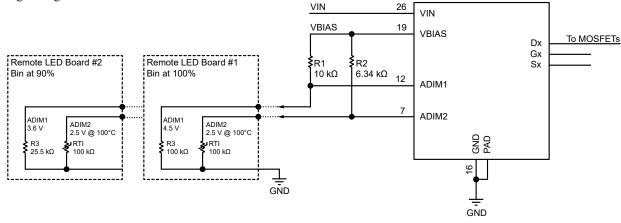

| LED Binning and NTC Derating2                             | <u>29</u> |

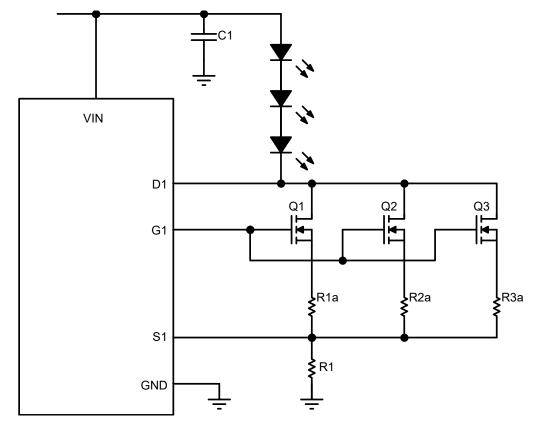

| Parallel MOSFET Arrangement for High-Power Application 3  | 31        |

| Arrangement to Avoid LED Current in External PWM Mode     |           |

| with Full Pin Connected to VIN and PWMINx Held Low        |           |

| at Startup                                                | 32        |

| Quick Summary of Operation                                | 33        |

| Package Outline Drawing                                   | 34        |

| Revision History                                          | 35        |

#### **ET-32 Package Terminals**

### TERMINAL DIAGRAM AND TERMINAL LIST

| Number | Name                                                                                                                                                                                                                                                                          | Function                                                                                                                                                                                 |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | D3                                                                                                                                                                                                                                                                            | Drain sensing for channel 3 for LED fault detection.                                                                                                                                     |

| 2      | S3                                                                                                                                                                                                                                                                            | Current sense for channel 3; connect sense resistor to GND to set peak current level.                                                                                                    |

| 3      | G3                                                                                                                                                                                                                                                                            | Gate driver for external N-channel MOSFET for channel 3.                                                                                                                                 |

| 4      | D4                                                                                                                                                                                                                                                                            | Drain sensing for channel 4 for LED fault detection.                                                                                                                                     |

| 5      | S4                                                                                                                                                                                                                                                                            | Current sense for channel 4; connect sense resistor to GND to set peak current level.                                                                                                    |

| 6      | G4                                                                                                                                                                                                                                                                            | Gate driver for external N-channel MOSFET for channel 4.                                                                                                                                 |

| 7      | ADIM2                                                                                                                                                                                                                                                                         | Voltage on this pin sets peak LED current. This pin can be used for external thermal derating using ar NTC, or "hybrid" analog and PWM dimming to extend the range of PWM duty cycles.   |

| 8      | nFAULT                                                                                                                                                                                                                                                                        | Open-drain active low fault flag output; also used as fault input when MODE is connected to VBIAS.                                                                                       |

| 9      | PWMOUT                                                                                                                                                                                                                                                                        | Replicated internal PWM dimming frequency and duty cycle signal for cascaded driver applications.<br>Leave PWMOUT pin open if it is not used. PWMOUT is not driven in external PWM mode. |

| 10     | FDIS                                                                                                                                                                                                                                                                          | VIN threshold for LED Open fault detection.                                                                                                                                              |

| 11     | VINDERAT                                                                                                                                                                                                                                                                      | Voltage at this pin sets VIN derating threshold.                                                                                                                                         |

| 12     | ADIM1                                                                                                                                                                                                                                                                         | Voltage on this pin sets peak LED current. This pin can be used for LED binning adjustment.                                                                                              |

| 13     | VDR                                                                                                                                                                                                                                                                           | Voltage on this pin sets the internal PWM dimming duty cycle.                                                                                                                            |

| 14     | UVLO                                                                                                                                                                                                                                                                          | Voltage at this pin sets the input voltage UVLO threshold.                                                                                                                               |

| 15     | 15 SLEW Controls rise and fall times of LED current. Tie to VBIAS to drive LEDs with 80 μs slew time<br>GND to drive LEDs with 6 μs slew time. Connect a resistor to GND to adjust slew time bell<br>range.                                                                   |                                                                                                                                                                                          |

| 16     | GND                                                                                                                                                                                                                                                                           | Ground.                                                                                                                                                                                  |

| 17     | FSET                                                                                                                                                                                                                                                                          | Sets internal PWM dimming frequency. Connect a resistor to GND to set internal PWM frequency;<br>connect to VBIAS when using external PWM.                                               |

| 18     | MODE                                                                                                                                                                                                                                                                          | Sets the fault handling mode. Tie to VBIAS for "one-out-all-out" or the GND for "one-out-continue". See Table 1.                                                                         |

| 19     | VBIAS                                                                                                                                                                                                                                                                         | Internal bias supply; connect to GND through a 2.2 $\mu\text{F}$ / 16 V ceramic capacitor. VBIAS pin can deliver up to 10 mA to an external load.                                        |

| 20     | S2                                                                                                                                                                                                                                                                            | Current sense for channel 2; connect sense resistor to GND to set peak current level.                                                                                                    |

| 21     | G2                                                                                                                                                                                                                                                                            | Gate driver for external N-channel MOSFET for channel 2.                                                                                                                                 |

| 22     | D2                                                                                                                                                                                                                                                                            | Drain sensing for channel 2 for LED fault detection.                                                                                                                                     |

| 23     | S1                                                                                                                                                                                                                                                                            | Current sense for channel 1; connect sense resistor to GND to set peak current level.                                                                                                    |

| 24     | G1                                                                                                                                                                                                                                                                            | Gate driver for external N-channel MOSFET for channel 1.                                                                                                                                 |

| 25     | D1                                                                                                                                                                                                                                                                            | Drain sensing for channel 1 for LED fault detection.                                                                                                                                     |

| 26     | VIN                                                                                                                                                                                                                                                                           | Input supply; place a 0.1 µF decoupling capacitor close to this pin.                                                                                                                     |

| 27     | <ul> <li>FULL Drive high to override PWM settings and force all enabled LED channels to 100% duty cycle;</li> <li>FULL for LEDs to operate in PWM mode. In external PWM mode, if any PWMINx pin is low at startu</li> <li>FULL pin must be low for at least 20 ms.</li> </ul> |                                                                                                                                                                                          |

| 28     | MINOUT                                                                                                                                                                                                                                                                        | Provides minimum drain voltage of enabled channels during LED on-time; use for feedback to adjust the output of a pre-regulator.                                                         |

| 29     | PWMIN1                                                                                                                                                                                                                                                                        | External PWM input for LED channel 1; tie this pin high for 100% duty cycle or to use internal dimming.                                                                                  |

| 30     | PWMIN2                                                                                                                                                                                                                                                                        | External PWM input for LED channel 2; tie this pin high for 100% duty cycle or to use internal dimming.                                                                                  |

| 31     | PWMIN3                                                                                                                                                                                                                                                                        | External PWM input for LED channel 3; tie this pin high for 100% duty cycle or to use internal dimming.                                                                                  |

| 32     | PWMIN4                                                                                                                                                                                                                                                                        | External PWM input for LED channel 4; tie this pin high for 100% duty cycle or to use internal dimming.                                                                                  |

| -      | PAD                                                                                                                                                                                                                                                                           | Exposed thermal pad; connect to external ground pad for better thermal performance.                                                                                                      |

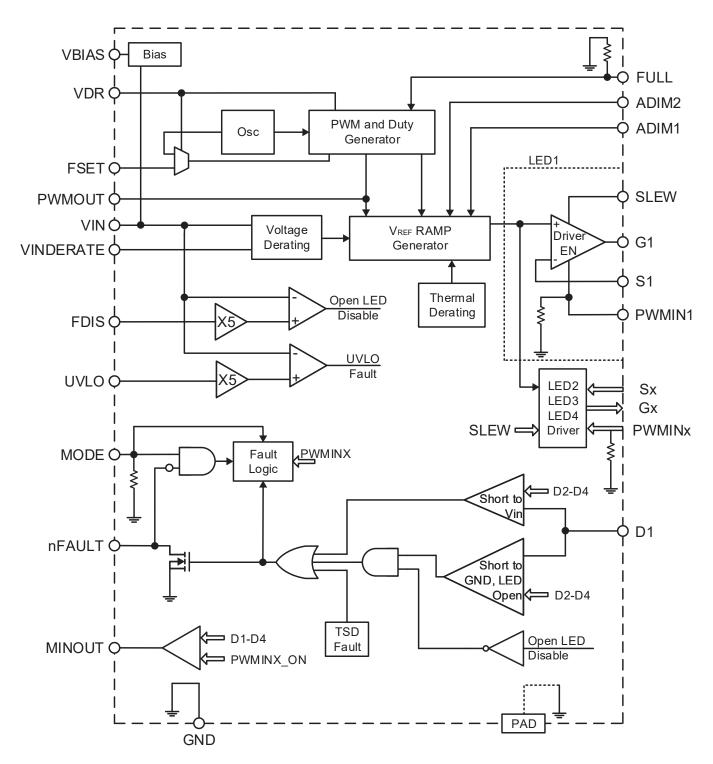

FUNCTIONAL BLOCK DIAGRAM

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

ELECTRICAL CHARACTERISTICS <sup>[1]</sup>: Unless otherwise specified, V<sub>IN</sub> = 12 V. "•" indicates specifications across the full operating temperature range of T<sub>J</sub> = -40°C to 150°C; other specifications are at T<sub>J</sub> = 25°C, unless noted otherwise. Refer to Figure 23 in application information section for typical application.

| Characteristics                                    | Symbol                 |                                                                                                                                    | Test Conditions                                                                                                                                                                                                                                    |   | Min. | Тур. | Max. | Unit |

|----------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|------|------|------|

| INPUT SUPPLY                                       |                        |                                                                                                                                    |                                                                                                                                                                                                                                                    |   |      |      |      |      |

| Operating Input Voltage Range                      | V <sub>IN</sub>        |                                                                                                                                    |                                                                                                                                                                                                                                                    | • | 5.3  | -    | 40   | V    |

| V <sub>IN</sub> Operational Current                | I <sub>INQ</sub>       | FULL = HIG                                                                                                                         | Н                                                                                                                                                                                                                                                  | • | -    | -    | 10   | mA   |

| Startup Time                                       | t <sub>on</sub>        | V <sub>SX</sub> = 20 mV                                                                                                            | $\label{eq:product} \begin{array}{l} \mu F, \ V_{\text{INDERAT}} = V_{\text{ADIMx}} = V_{\text{BIAS}}, \\ \prime \ (\text{A80804-1}), \ V_{\text{SX}} = 50 \ \text{mV} \ (\text{A80804}), \\ \ \mathcal{P} \text{WMINx toggled high}. \end{array}$ |   | _    | 100  | _    | μs   |

| CURRENT REGULATION                                 |                        |                                                                                                                                    |                                                                                                                                                                                                                                                    |   |      |      |      |      |

|                                                    |                        |                                                                                                                                    | V <sub>VINDERAT</sub> = V <sub>ADIMx</sub> = V <sub>VBIAS</sub>                                                                                                                                                                                    | • | 194  | 200  | 206  | mV   |

|                                                    |                        | A80804-1                                                                                                                           | $V_{VINDERAT} = V_{ADIMx} = V_{VBIAS}$<br>(T <sub>J</sub> = 125°C)                                                                                                                                                                                 |   | 196  | 200  | 204  | mV   |

| Sx Reference Voltage                               | V <sub>SENSE</sub>     |                                                                                                                                    | V <sub>VINDERAT</sub> = V <sub>ADIMx</sub> = V <sub>VBIAS</sub>                                                                                                                                                                                    | • | 485  | 500  | 515  | mV   |

|                                                    |                        | A80804                                                                                                                             | $V_{VINDERAT} = V_{ADIMx} = V_{VBIAS}$<br>(T <sub>J</sub> = 125°C)                                                                                                                                                                                 |   | 490  | 500  | 510  | mV   |

| Sx Reference Matching [1]                          | Err <sub>VSENSE</sub>  | No derating                                                                                                                        | · · · ·                                                                                                                                                                                                                                            |   | _    | -    | 2    | %    |

| Analog Dimming ADIM1 / VBIAS Ratio                 | ADIM1R                 | $V_{ADIM2} = V_{VB}$<br>$V_{SX} = 180 \text{ m}^3$                                                                                 | <sub>IAS</sub> , no derating,<br>V (A80804-1), V <sub>SX</sub> = 450 mV (A80804)                                                                                                                                                                   |   | -    | 0.72 | _    | _    |

| Analog Dimming ADIM2 / VBIAS Ratio                 | ADIM2R                 | $V_{ADIM1} = V_{VBIAS}$ , no derating,<br>$V_{SX} = 180 \text{ mV}$ (A80804-1), $V_{SX} = 450 \text{ mV}$ (A80804)                 |                                                                                                                                                                                                                                                    |   | -    | 0.45 | _    | _    |

| VBIAS                                              |                        |                                                                                                                                    |                                                                                                                                                                                                                                                    |   |      |      |      |      |

| VBIAS Pin Voltage                                  | V <sub>VBIAS</sub>     | I <sub>VBIAS</sub> = 0 to                                                                                                          | I <sub>VBIAS</sub> = 0 to 10 mA                                                                                                                                                                                                                    |   | 4.85 | 5.0  | 5.15 | V    |

| VBIAS Undervoltage Release                         | V <sub>VBIASUV</sub>   | V <sub>IN</sub> rising                                                                                                             |                                                                                                                                                                                                                                                    |   | -    | 4.5  | -    | V    |

| VBIAS Undervoltage Lockout Hysteresis              | V <sub>VBIASHYS</sub>  | IC disabled                                                                                                                        |                                                                                                                                                                                                                                                    |   | -    | 0.2  | -    | V    |

| GATE DRIVER                                        | •                      | ·                                                                                                                                  |                                                                                                                                                                                                                                                    |   |      | ·    |      |      |

| Gx High-Level Output                               | V <sub>GATEH</sub>     |                                                                                                                                    | Gx High, V <sub>SX</sub> = 180 mV (A80804-1)<br>50 mV (A80804)                                                                                                                                                                                     |   | 6    | -    | 9    | V    |

| Gx Low-Level Output                                | V <sub>GATEL</sub>     | FSET = VB                                                                                                                          | IAS, PWMIN = LOW                                                                                                                                                                                                                                   |   | -    | -    | 0.7  | V    |

| GATE Driver Dropout                                | V <sub>GATE_drop</sub> | V <sub>IN</sub> = 5.3 V, V<br>V <sub>SX</sub> = 450 m                                                                              | / <sub>SX</sub> = 180 mV (A80804-1) and<br>V (A80804), measured as (V <sub>IN</sub> – V <sub>GX</sub> )                                                                                                                                            |   | -    | -    | 1    | V    |

| Gate Pull-Up Current                               | I <sub>GPU</sub>       |                                                                                                                                    | IV (A80804-1) and<br>IV (A80804), V <sub>GX</sub> = 0 V, V <sub>IN</sub> = 7 V                                                                                                                                                                     |   | -    | -360 | -    | μA   |

| Gate Pull-Down Current                             | IGPD                   | $V_{SX} = 220 \text{ mV} (A80804-1) \text{ and}$<br>$V_{SX} = 550 \text{ mV} (A80804), V_{GX} = 7 \text{ V}, V_{IN} = 7 \text{ V}$ |                                                                                                                                                                                                                                                    |   | -    | 360  | -    | μA   |

| External FET Gate Capacitance Range <sup>[4]</sup> | C <sub>GISS</sub>      | For stable operation                                                                                                               |                                                                                                                                                                                                                                                    |   | 250  | -    | 2000 | pF   |

| Propagation Delay                                  | t <sub>pdi</sub>       | Delay from Internal PWM and PWMOUT pin during internal PWM mode.                                                                   |                                                                                                                                                                                                                                                    |   | -    | 2    | -    | μs   |

| Propagation Delay, External PWM Mode               | t <sub>pde</sub>       | Delay from PWMINx pin rising or falling level to Gx rising 3 V; C <sub>gate</sub> = 1 nF                                           |                                                                                                                                                                                                                                                    |   | -    | 2    | -    | μs   |

| PWM Matching During External PWM                   |                        | Duty cycle mismatch at 5%, 200 Hz PWM signal applied on PWMINx pins                                                                |                                                                                                                                                                                                                                                    |   | -    | -    | 6    | %    |

| PWM Dimming Frequency                              | f <sub>PWM</sub>       | R <sub>FPWM</sub> = 30                                                                                                             | 9 kΩ, across FSET to GND                                                                                                                                                                                                                           | • | 180  | 200  | 220  | Hz   |

Continued on the next page ...

# **High-Current Four-Channel Automotive LED Controller**

**ELECTRICAL CHARACTERISTICS**<sup>[1]</sup> (continued): Unless otherwise specified,  $V_{IN}$  = 12 V. "•" indicates specifications across the full operating temperature range of  $T_J$  = -40°C to 150°C; other specifications are at  $T_J$  = 25°C, unless noted otherwise. Refer to Figure 23 in application information section for typical application.

| Characteristics                                                                                    | Symbol                | ymbol Test Conditions                                                                                                  |                                                              |   | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---|------|------|------|------|

| GATE DRIVER (continued)                                                                            |                       | ·                                                                                                                      |                                                              |   |      | •    |      |      |

|                                                                                                    |                       | V <sub>DR</sub> driven by resistor                                                                                     | V <sub>VBIAS</sub> / V <sub>DR</sub> = 73 V,<br>SLEW = Low   |   | 1    | 2    | 3    | %    |

| Internal PWM Duty Cycle                                                                            | D <sub>PWML</sub>     | divider from VBIAS,<br>f <sub>PWM</sub> = 200 Hz,                                                                      | V <sub>VBIAS</sub> / V <sub>DR</sub> = 29.2 V,<br>SLEW = Low |   | 4.25 | 5    | 5.8  | %    |

| Internal P win Daty Gyold                                                                          | D <sub>PWMH</sub>     | V <sub>DR</sub> driven by resistor divider from VBIAS,                                                                 | SLEW = Low                                                   |   | 88   | 90   | 92   | %    |

|                                                                                                    | Ррумн                 | $V_{VBIAS} / V_{DR} = 1.62 V,$<br>$f_{PWM} = 200 Hz$                                                                   | SLEW = High                                                  |   | 88   | 90   | 92   | %    |

|                                                                                                    |                       | Rising or falling                                                                                                      | SLEW = High                                                  |   | 49   | 80   | 111  | μs   |

| Current Slew Time                                                                                  | t <sub>SLEW</sub>     | between 10% and<br>90% levels, for internal                                                                            | SLEW = Low                                                   |   | 4    | 8    | 12   | μs   |

|                                                                                                    |                       | reference ramp                                                                                                         | $R_{SLEW}$ = 100 k $\Omega$                                  |   | 14   | 25   | 36   | μs   |

| Disa Tima ta Fall Tima Matahing [2]                                                                | +                     | Rising or falling between<br>for internal PWM; SLEW                                                                    |                                                              |   | -    | 20   | -    | μs   |

| Rise Time to Fall Time Matching <sup>[2]</sup>                                                     | t <sub>SM</sub>       | Rising or falling between 10% and 90% levels,<br>for external PWM; SLEW = High                                         |                                                              |   | -    | 20   | -    | μs   |

| Rise Time and Fall Time Mismatch<br>Between Four Strings <sup>[3][4]</sup>                         | t <sub>SMS</sub>      | Rise and fall time misma<br>90% levels in four strings                                                                 |                                                              |   | -    | 3    | -    | %    |

| INTERNAL PWM POLYPHASE DELA                                                                        | λY                    | ·                                                                                                                      |                                                              |   |      |      |      |      |

| Poly-Phase Delay                                                                                   | t <sub>dpp</sub>      | Internal PWM, delay between rise and fall times<br>of successive outputs; measured at 50% V <sub>SENSE</sub><br>levels |                                                              |   | -    | 100  | -    | μs   |

| LOGIC PINS                                                                                         |                       |                                                                                                                        |                                                              |   |      |      |      |      |

| MODE, SLEW, FSET, PWMINX,<br>nFAULT, FULL Pins, Input Low Voltage                                  | V <sub>IL</sub>       | Below V <sub>IL</sub> level, input vol<br>logic low                                                                    | tage considered as                                           | • | 0.8  | _    | 1.1  | V    |

| MODE, SLEW, FSET, PWMINX,<br>nFAULT, FULL Pins, Input High Voltage                                 | V <sub>IH</sub>       | Above V <sub>IH</sub> level, input vo<br>logic high                                                                    | Itage considered as                                          | • | 1.5  | _    | 2    | V    |

| nFAULT, PWMOUT Pins,<br>Output Low Voltage                                                         | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA                                                                                                 |                                                              | • | _    | _    | 0.4  | V    |

| PWMOUT Pin, Output High Voltage                                                                    | V <sub>OH</sub>       | I <sub>OH</sub> = -1 mA                                                                                                |                                                              | • | 4    | _    | _    | V    |

| MODE, PWMINx, FULL, Pin Pull-<br>Down Resistor                                                     | R <sub>in</sub>       |                                                                                                                        |                                                              |   | -    | 100  | -    | kΩ   |

| PROTECTION                                                                                         |                       |                                                                                                                        |                                                              |   |      |      |      |      |

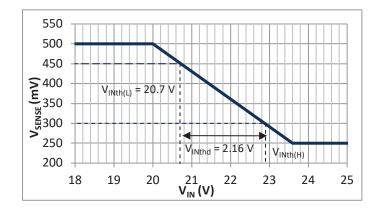

| Input Voltage Required to Derate<br>VSENSE by 10%                                                  | V <sub>INth(L)</sub>  | V <sub>INDERAT</sub> = 2 V                                                                                             |                                                              |   | 19.7 | 20.7 | 21.7 | V    |

| $V_{\text{IN}}$ Derating Range $(V_{\text{INth}(\text{H})} \text{ to } V_{\text{INth}(\text{L})})$ | V <sub>INthd</sub>    | V <sub>SENSE</sub> drops from 90% to 60% level                                                                         |                                                              |   | -    | 2.16 | -    | V    |

| Maximum V <sub>IN</sub> Derating for SENSE<br>Voltage                                              | V <sub>REF1</sub>     | $V_{\text{INDERAT}} = 2 \text{ V},  \text{V}_{\text{IN}} \ge 26 \text{ V}$                                             |                                                              |   | -    | 50   | -    | %    |

| VIN-to-Drain Short Detect Voltage                                                                  | V <sub>SCV</sub>      | Measured as $V_{IN} - V_{Dx}$ , Gx = PWMINx = high                                                                     |                                                              | • | 0.5  | 0.8  | 1.1  | V    |

| Open LED Fault Detect Voltage                                                                      | V <sub>OLED</sub>     | Measured at Dx, V <sub>IN</sub> > 5                                                                                    | × V <sub>FDSET</sub>                                         | • | 0.19 | 0.24 | 0.29 | V    |

| Open LED Disable Input Voltage                                                                     | V <sub>FDIS_VIN</sub> | V <sub>FDIS</sub> = 2 V                                                                                                |                                                              |   | -    | 10   | -    | V    |

Continued on the next page ...

# **High-Current Four-Channel Automotive LED Controller**

ELECTRICAL CHARACTERISTICS <sup>[1]</sup> (continued): Unless otherwise specified, V<sub>IN</sub> = 12 V. "•" indicates specifications across the full operating temperature range of T<sub>J</sub> = -40°C to 150°C; other specifications are at T<sub>J</sub> = 25°C, unless noted otherwise. Refer to Figure 23 in application information section for typical application.

| Characteristics                                                                     | Symbol                  | Test Conditions                                                                                         | Min. | Тур.                 | Max. | Unit   |

|-------------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------------------------------------------------|------|----------------------|------|--------|

| PROTECTION (continued)                                                              |                         |                                                                                                         |      |                      |      |        |

| PWM Frequency In Case Of Fault On<br>Faulty Channel (FULL and External<br>PWM Mode) | _                       | Open LED or Short to Drain fault                                                                        | _    | 500                  | _    | Hz     |

| PWM Duty Cycle In Case Of Fault On<br>Faulty Channel                                | _                       |                                                                                                         | _    | 5                    | _    | %      |

| Fault Detection Time (FULL Mode)                                                    | -                       | Open LED or Short to Drain fault                                                                        | _    | 6                    | _    | ms     |

| Fault Detection Cycles (PWM Mode)                                                   | -                       |                                                                                                         | _    | 3                    | -    | cycles |

| Fault reset time (FULL or External PWM)                                             | _                       |                                                                                                         | _    | 20                   | _    | ms     |

| Input Under Voltage Detect Voltage                                                  | V <sub>UVLO</sub>       | V <sub>UVLO</sub> = 2 V, V <sub>IN</sub> Falling (5×)                                                   | -    | 10                   | -    | V      |

| Input Under Voltage Detect Voltage<br>Hysteresis                                    | V <sub>UVLOhys</sub>    | V <sub>IN</sub> rising (fixed)                                                                          | -    | 0.8                  | -    | V      |

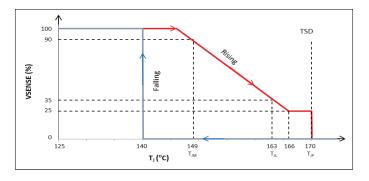

| Thermal Monitor Activation<br>Temperature <sup>[4]</sup>                            | T <sub>JM</sub>         | T <sub>J</sub> at V <sub>SENSE</sub> = 180 mV (A80804-1) and<br>V <sub>SENSE</sub> = 450 mV (A80804)    | -    | T <sub>JF</sub> – 21 | -    | °C     |

| Thermal Monitor Low Current<br>Temperature <sup>[4]</sup>                           | T <sub>JL</sub>         | T <sub>J</sub> at V <sub>SENSE</sub> = 70 mV (A80804-1) and<br>V <sub>SENSE</sub> = 175 mV (for A80804) | _    | T <sub>JF</sub> – 7  | _    | °C     |

| Overtemperature Shutdown <sup>[4]</sup>                                             | T <sub>JF</sub>         | Temperature increasing                                                                                  | -    | 170                  | -    | °C     |

| Overtemperature Hysteresis <sup>[4]</sup>                                           | T <sub>Jhys</sub>       | Recovery = T <sub>JF</sub> – T <sub>Jhys</sub>                                                          | -    | 30                   | -    | °C     |

| MINOUT                                                                              |                         |                                                                                                         |      |                      |      |        |

| MINOUT Internal Reference Voltage                                                   | V <sub>MINOUT</sub>     |                                                                                                         | -    | 0.8                  | -    | V      |

| MINOUT Drive Capability                                                             | IMINOUT                 |                                                                                                         | -    | ±100                 | -    | μA     |

| MINOUT Gain                                                                         | A <sub>MINOUT</sub>     |                                                                                                         | -    | 10                   | -    | -      |

| MIONOUT Offset                                                                      | V <sub>NIMOUT_off</sub> |                                                                                                         | -    | 0.5                  | -    | V      |

<sup>[1]</sup> Reference matching is defined as:  $(V_{SENSEmax} - V_{SENSEmin}) / V_{SENSE(AVG)}$ , where  $V_{SENSE(AVG)}$  is the average of all enabled  $V_{SENSEx}$ . <sup>[2]</sup> Rise Time to Fall Time Matching is defined as the maximum difference between the rise time and the fall time of the same string.

[3] Rise Time to Fall Time Mismatch Between Four Strings is defined as the maximum ratio of the difference between either the rise time or the fall time to the average of the rise time or fall times between four strings.

<sup>[4]</sup> Ensured by design and characterization.

# **High-Current Four-Channel Automotive LED Controller**

# FUNCTIONAL DESCRIPTION

The A80804 is a four-channel linear current regulator for LED driver applications using external N-channel MOSFETs to handle power dissipation in linear mode. The LED current in each channel can be programmed separately by selecting each current-sense resistor. Each channel also has a separate PWMINx pin to control external PWM dimming or act as an enable pin. The peak LED current can be further controlled by analog dimming using ADIM1 and ADIM2.

Internal PWM generation uses a resistor to ground on FSET to set the PWM frequency and a voltage on VDR to set the duty cycle, typically a resistor divider from VBIAS to ground. When using internal PWM, the PWM signal is replicated on the PWMOUT pin for cascading multiple A80804s together.

For external PWM mode, connect FSET to VBIAS and apply a PWM signal to each PWMINx pin. The PWMOUT pin stays low while using external PWM.

Extensive protections such as input undervoltage, MOSFET drain short-to-GND, drain short-to-VIN, LED open, and thermal shutdown are incorporated to protect the device and the LEDs. The A80804 also includes LED current derating for high input voltages, based on a programmable threshold, and high internal device temperature.

# **LED Current Sense Resistor**

LED peak current (100%) level can be set independently for each channel by selecting a proper resistor value from each Sx pin to GND as shown in Equation 1:

Equation 1:

```

I_{LEDpeak} = V_{SENSE} / R_{SENSE}

```

where  $V_{SENSE}$  is 500 mV for A80804 devices and 200 mV for A80804-1 devices,  $I_{LEDpeak}$  is in amps (A), and  $R_{SENSE}$  is in  $\Omega$ .

# **LED PWM Dimming**

A80804 can operate in external PWM mode where each channel can be individually controlled or in internal PWM dimming mode with automatic phase shifting. Tie the FSET pin to VBIAS to use external PWM mode or tie to GND through a resistor for internal PWM mode.

## **External PWM Dimming**

When FSET is tied to VBIAS, the A80804 operates in external PWM mode. A logic-level input signal can be used to control each PWMINx pin to set each respective channel's PWM

frequency and duty cycle, allowing each channel to be dimmed independently.

The external PWM frequency should be between 200 Hz and 1000 Hz with a duty cycle between 5% and 100%. While in external PWM mode, the PWMOUT pin will stay low.

The LEDs turn on when each respective PWMINx signal is high. The LED current slew rate is controlled through the SLEW pin and the same slew control is applied to all channels.

For wider dimming ratios, external PWM dimming can be combined with analog dimming.

#### Internal PWM Dimming

To use the A80804 with internal PWM dimming and automatic phase shifting between each channel, tie the FSET pin to GND through a resistor to set the PWM frequency. The internal PWM frequency range is 100 to 1000 Hz. Use Equation 2 to calculate the resistor value for a PWM frequency.

Equation 2:

$$R_{FPWM} = 5400 / (f_{PWM} - 25)$$

where  $f_{PWM}$  is in Hz and  $R_{FPWM}$  is in k $\Omega$ .

For example, for  $f_{PWM} = 200$  Hz, use a 30.9 k $\Omega$  resistor.

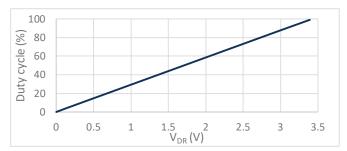

The internal PWM dimming duty cycle is set with a voltage on the VDR pin. The PWM duty cycle depends on the ratio of the voltage at the VDR and VBIAS pins. For better accuracy, use a voltage divider from VBIAS to VDR. The internal duty cycle range is 2% to 90%. See Equation 3 and Figure 2.

Equation 3:

$$DUTY = 146 \times V_{DR} / V_{BIAS}$$

where  $V_{\text{DR}}$  and  $V_{\text{BIAS}}$  are in volts and DUTY is the duty cycle in percent.

Figure 2: Relationship of External Voltage Input on VDR Pin and Dimming Duty Cycle.  $V_{DR}$  can be varied from 0 to 3.6 V.

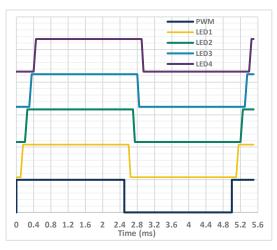

#### **Internal PWM Phase Shift**

While operating in internal PWM mode, the signal sent to the first channel is delayed 100  $\mu$ s (typical) from the internal reference PWM signal, and each subsequent channel is delayed another 100  $\mu$ s (typical) from the previous channel to minimize di/dt and improve EMI. If any channel is not used, the delay for the remaining channels will remain the same. For example, if channel 1 and 2 are not used, channel 3 and 4 will still be delayed by 300  $\mu$ s and 400  $\mu$ s with respect to the internal PWM signal.

Equation 4:

$$t_{CHDELAY} = 100 \ \mu s \times N$$

where N is the channel number.

#### Figure 3: Polyphase Operation with Internal PWM

The polyphase behavior is disabled in external PWM mode since each channel can be independently controlled, and each channel's PWMINx signal can be time-shifted to achieve polyphase operation.

# Full Mode

When the FULL pin is pulled high, the A80804 ignores the PWM configuration and operates at 100% duty cycle. The FULL pin does not affect the analog dimming level.

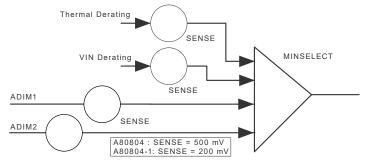

# **Analog Dimming**

Analog dimming is available through ADIM1 and ADIM2. Each ADIMx pin can be tied to VBIAS to disable the dimming for that ADIM pin. When not tied to VBIAS, the voltage on ADIMx scales  $V_{SENSE}$ , the internal reference voltage that is maintained across  $R_{SENSE}$ . The lower of the two ADIMx options will determine the dimming level. Analog dimming is ratiometric to  $V_{BIAS}$ .  $V_{ADIM1}$  is

the voltage at ADIM1, and  $V_{ADIM2}$  is the voltage at ADIM2. The  $V_{SENSE}$  reference voltage is also affected by Input Overvoltage Derating and Thermal Derating and Protection Shutdown, and the  $V_{SENSE}$  level for regulation is the minimum of all of these circuits.

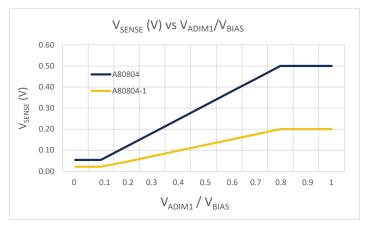

#### Analog Dimming with ADIM1

An analog voltage on ADIM1 can be used to derate the peak LED current for binning or other application requirements. While ADIM2 is at  $V_{BIAS}$ , to disable dimming on ADIM2, the reference voltage  $V_{SENSE}$  scales with ADIM1 based on Equation 5. Use Equation 6 to find the voltage at ADIM1 for a targeted dimming level.

Equation 5:

$$V_{SENSE} = 0.6371 \times (V_{ADIM1}/V_{BIAS}) - 0.0097 \text{ (A80804)}$$

$$V_{SENSE} = 0.2571 \times (V_{ADIM1}/V_{BIAS}) - 0.0057 \text{ (A80804-1)}$$

where  $V_{ADIM2} = V_{BIAS}$ .

Equation 6:

$V_{ADIM1} = (V_{BIAS} \times (500 \text{ mV} \times DimPct + 0.0097)) / 0.637 (A80804)$

$V_{ADIM1} = \left(V_{BIAS} \times (200 \text{ mV} \times DimPct + 0.0057)\right) / 0.2571 \text{ (A80804-1)}$

where  $V_{ADIM2} = V_{BIAS}$  and DimPct is the dimming percentage target, scaled from 0 to 1.

To use analog dimming with ADIM1, set  $V_{ADIM1}$  between 10% and 80% of  $V_{BIAS}$ ; see Figure 4.

Figure 4: Effect of ADIM1 on V<sub>SENSE</sub>

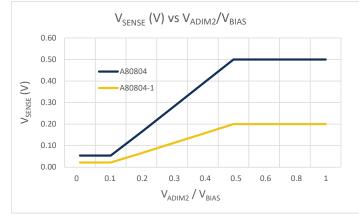

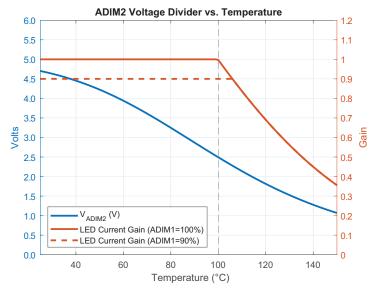

#### Analog Dimming with ADIM2

An analog voltage on ADIM2 can be used to derate the peak LED current, for example with an NTC thermistor to derate the current at high LED temperatures. To use analog dimming with ADIM2,

set  $V_{ADIM2}$  between 10% to 50% of  $V_{BIAS}$ ; there is no derating when  $V_{ADIM2}$  is higher than  $V_{BIAS}$  / 2. See Equation 7 to calculate  $V_{SENSE}$  and Equation 8 to calculate the ADIM2 pin voltage for a targeted dimming ratio.

Equation 7:

$V_{SENSE} = 1.125 \times (V_{ADIM2}/V_{BIAS}) - 0.0625 \text{ (A80804)}$  $V_{SENSE} = 0.450 \times (V_{ADIM2}/V_{BIAS}) - 0.025 \text{ (A80804-1)}$

where  $V_{ADIM1} = V_{BIAS}$ , and  $V_{ADIM2} / V_{BIAS} < 0.5$ .

Equation 8:

$V_{ADIM2} = (V_{BIAS} \times (500 \text{ mV} \times DimPct + 0.0625)) / 1.125 \text{ (A80804)}$  $V_{ADIM2} = (V_{BIAS} \times (200 \text{ mV} \times DimPct + 0.025)) / 0.450 \text{ (A80804-1)}$

Figure 5: Effect of ADIM2 on V<sub>SENSE</sub>

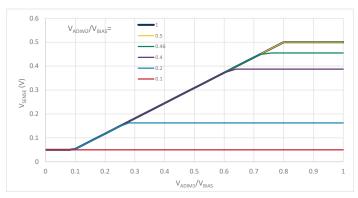

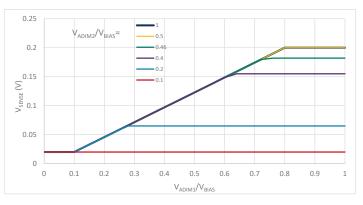

When both ADIM1 and ADIM2 are used,  $\rm V_{\rm SENSE}$  is the minimum of ADIM1 and ADIM2.

Figure 6: Combined Effect of ADIM1 and ADIM2 pin voltages on V<sub>SENSE</sub> for A80804

Figure 7: Combined Effect of ADIM1 and ADIM2 pin voltages on V<sub>SENSE</sub> for A80804-1

# **LED Current Slew Control**

The LED current rise and fall times can be controlled with the SLEW pin. This allows the system designer to optimize for PWM duty cycle accuracy or EMI performance. When SLEW is tied to logic high, the 10% to 90% slew time is 80  $\mu$ s, the slowest slew rate option. When SLEW is connected to logic low, the slew time is 6  $\mu$ s, the fastest slew rate option. For a slew rate between the low and high levels, connect SLEW to GND through a resistor using Equation 9.

Equation 9:

$$t_{SLEW} = R_{SLEW} / 4$$

where  $t_{SLEW}$  is in  $\mu$ s and  $R_{SLEW}$  is in  $k\Omega$ . Use a value of  $R_{SLEW}$  between 324 k $\Omega$  (80  $\mu$ s) and 24.3 k $\Omega$  (6  $\mu$ s).

# PWMOUT

The A80804 has a PWMOUT pin that replicates the reference PWM signal used while in internal PWM mode. This signal can be used as the PWMINx signal for slave devices to synchronize the slave device with the master device. Since the PWMINx pins are driven from PWMOUT, the slave device must operate in external PWM mode. Therefore, the slave device will not have the PWM channel phase shifting but uses the master's internal PWM reference which is 100  $\mu$ s ahead of the channel 1 on the master; see the Multiple A80804 Master-Slave Arrangement application.

PWMOUT is low while in external PWM mode.

Equation 11.

## MINOUT

The MINOUT pin provides an output voltage proportional to the minimum voltage of the Dx pins for all active channels. The voltage from MINOUT can be fed to a voltage regulator's feedback pin to complete a closed-loop system and trim the regulated output leading to the LEDs. The voltage on MINOUT is given by Equation 10 with minimum of 0.3 V (typical) and maximum of 3.5 V (typical).

Equation 10:

$$V_{MINOUT} = 10 \times (V_{Dx MIN} - 0.8) + 0.3$$

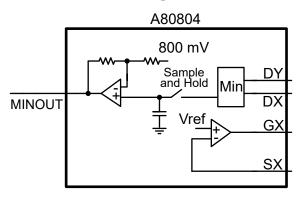

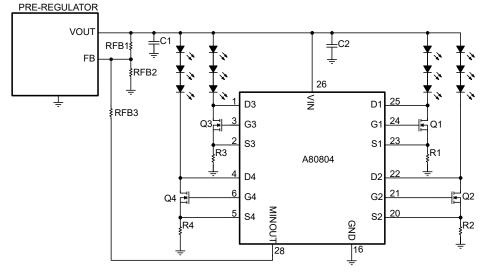

Figure 8: Block Diagram of MINOUT Block

An example of a pre-regulator powering the LED strings is shown in Figure 9. The MINOUT signal feeds into the regulator control loop through an external resistor, RFB3. Equation 11 can be used to calculate the resistor values.

$$R_{FB3} = \left[\frac{V_{MINOUT(\max)} \times (V_{OUT(\max)} - V_{FB})}{V_{FB} \times (V_{OUT(\max)} - V_{OUT(\min)})} - 1\right] \times R_{FB2}$$

$$R_{FB1} = \left[\frac{V_{OUT(\max)} - V_{FB}}{V_{FB}}\right] \times \left[\frac{R_{FB2} \times R_{FB3}}{R_{FB2} + R_{FB3}}\right]$$

$V_{OUT(min)}$  and  $V_{OUT(max)}$  are the worst-case required voltages for the LEDs to operate, and  $V_{FB}$  is the feedback voltage of the pre-regulator.

## **Protection Functions**

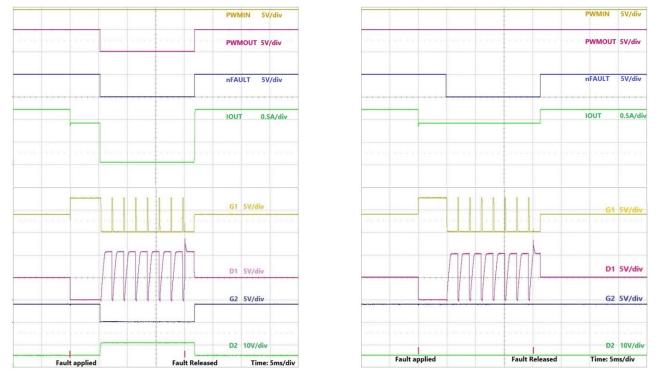

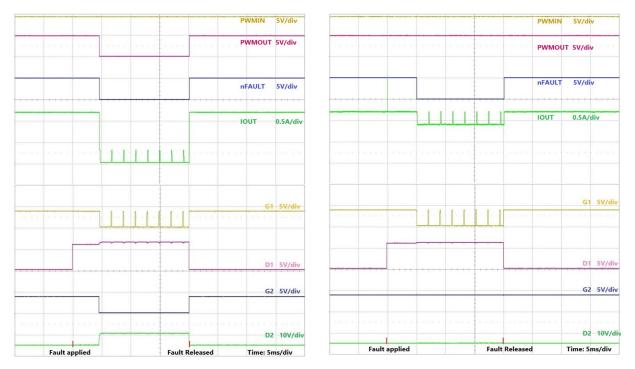

The A80804 asserts a fault by pulling the nFAULT pin low when a fault is detected for three consecutive PWM cycles. The 3-cycle count prevents fault assertion on a spurious transient. The device returns to normal operation immediately after the fault is removed. Any faulted LED string operates at 5% duty cycle during the PWM on-time to minimize power dissipation in the MOS-FETs and detect fault recovery. While in FULL mode, the device waits 6 ms to assert the nFAULT pin low. While in external PWM mode or FULL mode, the faulted LED string is driven with a 500 Hz, 5% duty cycle PWM signal to detect fault recovery.

#### **MODE Pin Behavior**

When a fault occurs on one LED string, the behavior of other strings is determined by the state of the MODE pin. Other strings

Figure 9: Example of Using MINOUT with Pre-regulator

continue to operate normally when MODE is low ("one-out-continue" or "N-1" mode) and shutdown when MODE is high ("oneout-all-out" mode). The nFAULT pin becomes bidirectional and acts as both a fault input and output when MODE is high, which can be used to pass the fault state to slave or paralleled devices.

### FDIS Pin for Fault Disable

Open LED and MOSFET drain short-to-GND faults are disabled when the input voltage is less than five times the voltage at the FDIS pin,  $V_{IN} < 5 \times V_{FDIS}$ . Select a  $V_{FDIS}$  level higher than the LED string's forward voltage to prevent faults during startup or  $V_{IN}$  transients.

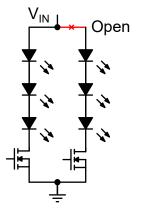

#### **OPEN LED**

An open LED fault is detected when  $V_{IN}$  > 5  $\times$   $V_{FDIS}$  and  $V_{Dx}$  < 0.24 V.

Once the fault is detected, nFAULT is asserted low and that LED channel operates with 5% duty cycle even if FULL is high, keeping the MOSFET on with a low duty cycle to detect removal of the fault for auto-recovery. The LED current in the faulted string is zero since the LED current path is open. When the fault is removed,  $V_{Dx} > 0.24$  V, the device returns to normal operation.

Figure 10: LED Open Protection

If MODE is high, all other gates, Gx, and PWMOUT are pulled low once the fault is detected; parallel or slave devices will also turn off when nFAULT goes low if MODE is high, or when PWMOUT is pulled low if cascading PWMOUT to PWMINx of another device. If MODE is low all other gates, Gx, and PWM-OUT are unaffected and continue to operate normally.

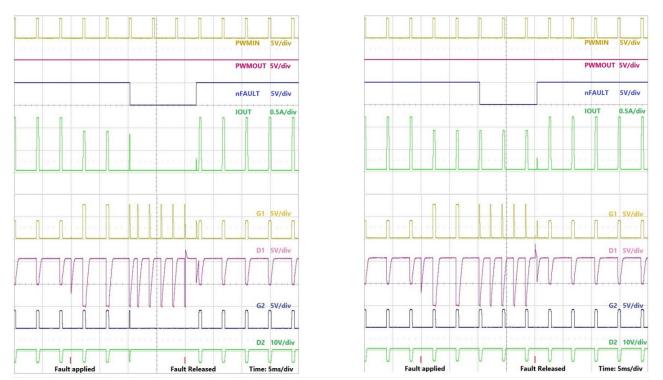

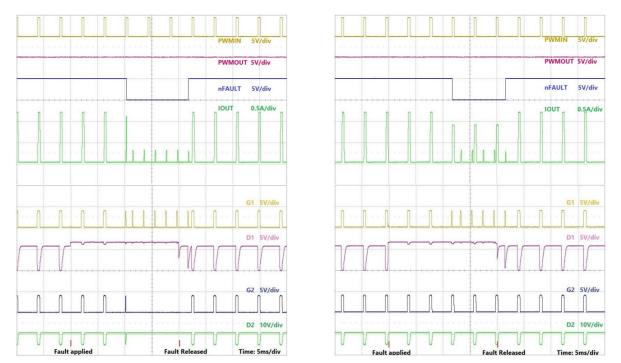

Figure 11: Open LED Fault on D1 in FULL mode. MODE = High (left), MODE = Low (right). Fault on channel 1.

Figure 12: Open LED Fault on D1 with External PWM. Fault on channel 1. MODE = High (left), MODE = Low (right).

Figure 13: Open LED Fault on D1 with Internal PWM. Fault on channel 1. MODE = High (left), MODE = Low (right).

#### Short Circuit Protection

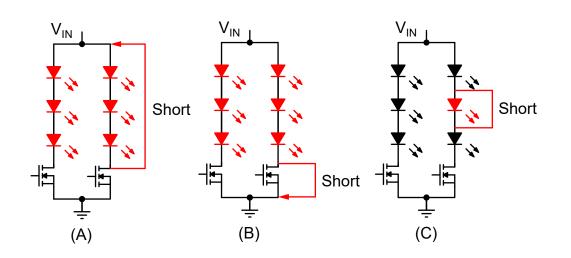

The A80804 can protect against multiple short-circuit faults scenarios, as shown in Figure 14.

### **Drain Short To GND**

A MOSFET drain short-to-ground fault is detected when  $V_{IN} > 5 \times V_{FDIS}$  and  $V_{Dx} < 0.24$  V. Once the fault is detected, nFAULT is asserted low and that LED channel operates with 5% duty cycle, even if FULL is high, to detect fault removal for autorecovery. The drain short-to-ground fault is not a latched fault. When the fault is removed,  $V_{Dx} > 0.24$  V, the device returns to normal operation. If MODE is high, all other gates, Gx, and PWMOUT are pulled low when the fault is detected; parallel or slave devices will also turn off when nFAULT goes low if the nFAULT pins are tied together and MODE is high. If MODE is low, the other gates and PWMOUT are unaffected and continue to operate normally. During a drain short-to-ground fault, the LED string may see a large current as the LED string is shorted to ground.

The operating waveforms Gx, Dx, PWMOUT, and nFAULT, are the same for drain short-to-GND fault and open LED fault except

the faulty LED string will see large current when the drain is shorted to ground.

### **Drain Short To VIN**

A MOSFET drain short-to-VIN, a full LED string short, is detected when  $(V_{IN} - V_{Dx}) < 0.8$  V and the configured LED current slew time has elapsed while PWMINx is high. Once the fault is detected, nFAULT is asserted low and that LED channel operates with 5% duty cycle even if FULL is high, keeping the MOSFET on with a low duty cycle to detect removal of the fault for auto-recovery and minimize power dissipation in the faulty LED string. The drain short-to-VIN fault is not a latched fault. When the fault is removed,  $(V_{IN} - V_{Dx}) > 0.8$  V, the device returns to normal operation. The current in the faulted LED string during the fault will be zero since the LED string is shorted out when the MOSFET drain is shorted to VIN.

If MODE is high, all other gates, Gx, and PWMOUT are pulled low once the fault is detected; parallel or slave devices will also turn off when nFAULT goes low if the nFAULT pins are tied together and MODE is high. If MODE is low, all other gates, Gx, and PWMOUT are unaffected and continue to operate normally.

**Figure 14: Short-Circuit Protection**

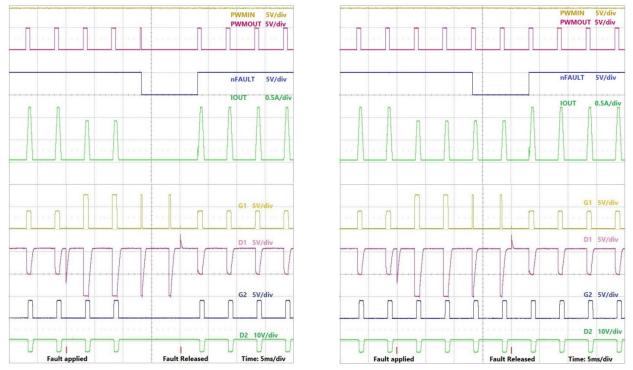

Figure 15: Drain Short to VIN Fault on D1 in FULL mode. MODE = High (left), MODE = Low (right).

Figure 16: Drain Short to VIN Fault on D1 with External PWM Dimming. MODE = High (left), MODE = Low (right).

Figure 17: Drain Short to VIN Fault on D1 with Internal PWM Dimming. MODE = High (left), MODE = Low (right).

#### **LED Short Response**

If less than the full LED string is shorted, the A80804 continues to work normally. This will lead to increased power dissipation in the LED string's MOSFET.

#### Input Undervoltage Protection

When input voltage,  $V_{IN}$ , is below the undervoltage lockout threshold defined by five times the voltage on the UVLO pin,  $V_{IN}$ < 5 ×  $V_{UVLO}$ , an input undervoltage fault is detected. If MODE is high while an undervoltage fault occurs, the device is off, and if MODE is low, the device stays on. The fault flag nFAULT is not affected by this fault.

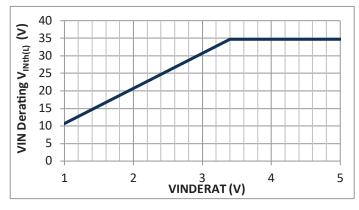

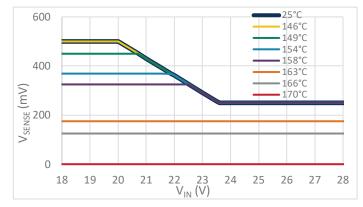

#### Input Overvoltage Derating

The A80804 can derate the LED current at higher input voltages to limit the power dissipation in the MOSFETs. The input voltage level to start derating,  $V_{INth(L)}$ , is ten times the voltage at the VIN-DERAT pin plus 0.7 V,  $10 \times V_{VINDERAT} + 0.7$  V, and is typically set with a resistor divider from VBIAS pin to VINDERAT pin. The level for maximum derating,  $V_{INth(H)}$  is higher than  $V_{INth(L)}$  by  $V_{INthd}$  (typically 2.16 V). The reference voltage,  $V_{SENSE}$ , decreases to 90% of its nominal value at  $V_{INth(L)}$  and to 60% at  $V_{INth(H)}$ ; see Figure 18 and Figure 19. The maximum derating is 50% for higher input voltage levels. See Equation 12 to calculate the voltage at

VINDERAT pin for a target V<sub>INth(L)</sub> level.

Equation 12:

$$V_{VINDERAT} = (V_{INth(L)} - 0.7) / 10$$

For example, when  $V_{VINDERAT} = 2.0 \text{ V}$ ,  $V_{SENSE}$  will derate to 90% of its nominal value when  $V_{IN} = 20.7 \text{ V}$ .

Even if the VINDERAT pin is tied to VBIAS, the A80804 will begin derating the LED current at 35 V (typical).

Figure 18: V<sub>INDERAT</sub> Voltage versus V<sub>IN</sub> Derating Threshold

#### Figure 19: Output Current Foldback Based on VIN

#### **Thermal Derating and Protection Shutdown**

At higher temperatures, the A80804 will derate the LED current to limit power dissipation in the external MOSFETs. The reference voltage,  $V_{SENSE}$ , decreases with increasing  $T_J$  as shown in Figure 20, where  $V_{SENSE}$  derates to 90% at 149°C (typical) and 35% at 163°C (typical). The maximum thermal derating is 25% of the nominal current. Thermal shutdown ( $T_{SD}$ ) completely disables the outputs under extreme overtemperature conditions (>170°C), and nFAULT goes low. The A80804 restarts when the temperature drops by 30°C.

Figure 20: Output Current Foldback Based on Rising T<sub>J</sub>

The combined effect of  $\mathrm{V}_{\mathrm{IN}}$  and thermal derating is shown in Figure 21.

#### Figure 21: Combined Effect of V<sub>IN</sub> Derating and Thermal Derating

LED peak current also depends on voltage on ADIMx pin even during  $\rm V_{\rm IN}$  and thermal derating.

#### Shutdown

While operating in internal PWM mode, each LED channel resets when its corresponding PWMINx pin is pulled low. While operating in external PWM mode, each LED channel resets when its corresponding PWMINx pin is pulled low for more than 20 ms.

When a channel is reset, its corresponding gate is pulled low and any faults associated with that channel are reset. The rest of the device operates normally. If a faulty string is disabled by pulling PWMINx pin low for greater than 20 ms, the device returns to normal operation for remaining channels and nFAULT is released.

#### Table 1: Fault Operation and Derating (Internal PWM mode)

|                         | nFAULT       |             | MODE = VBIAS                                                                                                                                                                                                                                                                                                                                                            |                                | MODE = Low                                                                                                                                                                                                                                                                                                                                       |

|-------------------------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | NFAULI       | PWMOUT      | Operation                                                                                                                                                                                                                                                                                                                                                               | PWMOUT                         | Operation                                                                                                                                                                                                                                                                                                                                        |

| Drain Shorted<br>to VIN | Low          | Low         | Detected for three consecutive PWM cycles when $(V_{IN} - V_{Dx}) < 0.8 \text{ V}$ . The faulty MOSFET remains on with 5% PWM. Other strings, PWMOUT, and nFAULT pulled low once fault detected. The fault is not latched. The faulty MOSFET will drop the full input voltage during PWM on-time. The device recovers to normal operation when the fault is removed.    | Normal                         | Detected for three consecutive PWM<br>cycles when $(V_{IN} - V_{Dx}) < 0.8$ V. The faulty<br>MOSFET remains on with 5% PWM, rest<br>of IC operates normally except nFAULT<br>pin is pulled low. The faulty MOSFET drop<br>full input voltage during PWM on-time. The<br>device recovers to normal operation when<br>the fault is removed.        |

|                         | The fault is | detected wh | en corresponding PWMIN pin is high and the con                                                                                                                                                                                                                                                                                                                          | ifigured slew tir              | ne has elapsed.                                                                                                                                                                                                                                                                                                                                  |