# Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

### FEATURES AND BENEFITS

- ASIL A functional safety

- □ Developed in accordance with ISO 26262

- □ Internal diagnostics and a defined Safe State

- $\square$  A<sup>2</sup>-SIL<sup>TM</sup> documentation available

- Highly programmable

- $\hfill\square$  Magnetic polarity, switch points, and hysteresis

- □ Temperature coefficient (supports SmCo, NdFeB, and ferrite magnets)

- □ Output polarity and current levels

- Reduces module bill of materials (BOM) and assembly cost

- □ Integrated overvoltage clamp (40 V load dump) and reverse-battery diode

- Integrated series resistor and bypass capacitor (UC package)

- $\hfill\square$  Enables PCB-less sensor modules

- Automotive-grade ruggedness and fault tolerance

- □ Extended AEC-Q100 qualification

- □ Operation from -40°C to 175°C junction temperature

- $\hfill\square$  3 to 24 V operating voltage range

- □ High EMC/ESD immunity

- □ Overtemperature indication

### PACKAGES

3-pin SOT23-W (LH)

### DESCRIPTION

APS11900 devices are highly programmable, two-wire planar Hall-effect sensor integrated circuits (ICs) developed in accordance with ISO 26262. They include internal diagnostics and support a functional safety level of ASILA. The enhanced two-wire currentmode interface provides interconnect open/short diagnostics and adds a Safe State to communicate diagnostic information while maintaining compatibility with legacy two-wire systems. Twowire sensors are well-suited to safety applications, especially those involving long wire harnesses.

Programming can be performed at the end of the line to optimize the sensor on a per unit or per module basis. The user can select the magnetic switch points, temperature coefficient, and hysteresis, and whether the device responds to north or south magnetic fields (unipolar switch) or both (bipolar latch or omnipolar switch). The response can be matched to SmCo, NdFeB, or low-cost ferrite magnets. There is a choice of two output current levels and either output polarity. In addition to a benchtop programmer (ASEK) for development and evaluation, universal software drivers are available to facilitate programming in a production environment.

Continued on the next page ...

### TYPICAL APPLICATIONS

- Automotive and industrial safety systems

- Seat position detection

- Seat belt buckles

- Hood/trunk/door latches

- Sunroof/convertible top/tailgate/liftgate actuation

- Brake/clutch pedals

- Electric power steering (EPS)

- Transmissions and shift selectors

- Wiper motors

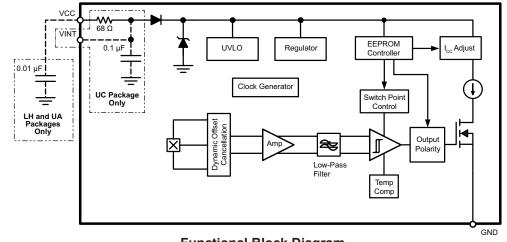

#### **Functional Block Diagram**

#### **DESCRIPTION** (continued)

APS11900 sensors are engineered to operate in the harshest environments with minimal external components. They are qualified beyond the requirements of AEC-Q100 Grade 0 and will survive extended operation at 175°C junction temperature. These monolithic ICs include on-chip reverse-battery protection, overvoltage protection (40 V load dump), ESD protection, overtemperature detection, and an internal voltage regulator for operation directly from an automotive battery bus. These integrated features reduce the end-product bill of materials (BOM) and assembly cost. The available SIP package with integrated discrete components (UC) enables PCB-less applications by incorporating all of the EMC protection components into the IC package. Other package options include industry-standard surface-mount SOT (LH) and throughhole SIP (UA) packages. All three packages are RoHS-compliant and lead (Pb) free with 100% matte-tin-plated leadframes.

For situations where a functionally equivalent but factory-programmed two-wire switch or latch is preferred, refer to the APS11500 and APS12400 device families, respectively.

#### SELECTION GUIDE

| Part Number    | Package Packing <sup>[1]</sup>                                     |                                 | Operating Ambient Temperature,<br>T <sub>A</sub> (°C) |

|----------------|--------------------------------------------------------------------|---------------------------------|-------------------------------------------------------|

| APS11900LLHALT | 00LLHALT 3-pin SOT23-W surface mount 7-inch reel, 3000 pieces/reel |                                 |                                                       |

| APS11900LLHALX | 3-pin SOT23-W surface mount                                        | 13-inch reel, 10000 pieces/reel |                                                       |

| APS11900LUAA   | 3-pin SIP through-hole                                             | Bulk, 500 pieces/bag            | -40 to 150                                            |

| APS11900LUCDTN | 3-pin SIP through-hole<br>with integrated passive components       | 13-inch reel, 4000 pieces/reel  |                                                       |

<sup>[1]</sup> Contact Allegro for additional packing options.

### SPECIFICATIONS

#### ABSOLUTE MAXIMUM RATINGS

| Characteristic                           | Symbol               | Notes         | Rating     | Unit   |

|------------------------------------------|----------------------|---------------|------------|--------|

| Supply Voltage <sup>[1]</sup>            | V <sub>CC</sub>      |               | 40         | V      |

| Reverse Supply Voltage                   | V <sub>RCC</sub>     |               | -23        | V      |

| Magnetic Flux Density                    | В                    |               | Unlimited  | G      |

| Maximum Number of EEPROM<br>Write Cycles | EEPROMW(max)         |               | 100        | cycles |

| Movimum Junction Townsrature             | T (mov)              |               | 165        | °C     |

| Maximum Junction Temperature             | T <sub>J</sub> (max) | For 500 hours | 175        | °C     |

| Storage Temperature                      | T <sub>stg</sub>     |               | –65 to 170 | °C     |

<sup>[1]</sup> This rating does not apply to extremely short voltage transients such as load dump and/or ESD. Those events have individual ratings specific to the respective transient voltage event. Contact your local field applications engineer for information on EMC test results.

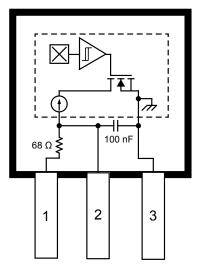

#### INTERNAL DISCRETE COMPONENT RATINGS (UC Package Only)

|           |                     |                               |                                         | Cha              | racteristics       |                      |                         |

|-----------|---------------------|-------------------------------|-----------------------------------------|------------------|--------------------|----------------------|-------------------------|

| Component | Symbol              | Test Conditions               | Rated Nominal<br>Resistance/Capacitance | Rated<br>Voltage | Rated<br>Tolerance | Rated Temp.<br>Range | Rated Power<br>Handling |

| Resistor  | R <sub>SERIES</sub> | In series with VCC            | 68 Ω                                    | 50 V             | ±15%               | -                    | 1/8 W                   |

| Capacitor | C <sub>SUPPLY</sub> | Connected between VCC and GND | 100 nF                                  | 50 V             | ±10%               | X7R                  | -                       |

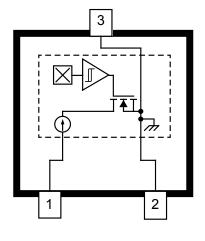

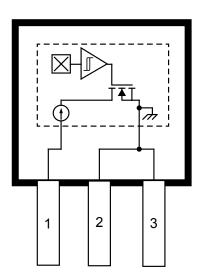

### PINOUT DIAGRAMS AND TERMINAL LIST TABLES

| Number | Package Nan |     | Function        |

|--------|-------------|-----|-----------------|

| Number | LH          | UA  | Function        |

| 1      | VCC VCC     |     | Supply voltage  |

| 2      | GND GND     |     | Ground terminal |

| 3      | GND         | GND | Ground terminal |

Note: For best performance, tie Pins 2 and 3 together close to the IC.

LH Package, 3-Pin SOT23W Pinout

UA Package, 3-Pin SIP Pinout

| Terminal List Table (UC Package) |              |                                                                                                                                  |  |  |  |  |

|----------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Number                           | Package Name | Function                                                                                                                         |  |  |  |  |

| Number                           | UC           | Function                                                                                                                         |  |  |  |  |

| 1                                | VCC          | Supply voltage                                                                                                                   |  |  |  |  |

| 2                                | VINT         | This pin reflects the internal voltage, V <sub>INT</sub> , after the internal series resistor. This pin should be kept floating. |  |  |  |  |

| 3                                | GND          | Ground terminal                                                                                                                  |  |  |  |  |

UC Package, 3-Pin SIP Pinout

## **Two-Wire End-of-Line Programmable** Hall-Effect Switch/Latch

#### ELECTRICAL CHARACTERISTICS: Valid over full operating voltage and ambient temperature ranges for T<sub>J</sub> < T<sub>J</sub>(max) and $C_{BYP} = 0.01 \ \mu F$ , unless otherwise specified

| Characteristics                       | Symbol                 | Test Conditions                                                                             |                    | Min.    | Typ. <sup>[3]</sup> | Max. | Unit  |

|---------------------------------------|------------------------|---------------------------------------------------------------------------------------------|--------------------|---------|---------------------|------|-------|

| Supply Voltage                        | V <sub>cc</sub>        | Operating, T <sub>J</sub> < 165°C                                                           | LH and UA packages | 3.0     | -                   | 24   | V     |

|                                       |                        | Operating, T <sub>J</sub> < 165°C                                                           | UC package         | 4.4 [4] | -                   | 24   | V     |

|                                       | V <sub>CC(UV)DIS</sub> | After power-on, as V <sub>CC</sub> increases, output is forced to POS until this voltage is | LH and UA packages | _       | 2.6                 | _    | V     |

| Lindom (altorna Lina) (a)             | 00(01)210              | reached                                                                                     | UC package         | _       | 3.5                 | _    | V     |

| Undervoltage Lockout <sup>[4]</sup>   | V <sub>CC(UV)EN</sub>  | After POK, when V <sub>CC</sub> drops below this voltage, output is forced to POS           | LH and UA packages | _       | 2.3                 | _    | V     |

|                                       |                        | Voltage, output is forced to POS                                                            | UC package         | _       | 3.2                 | _    | V     |

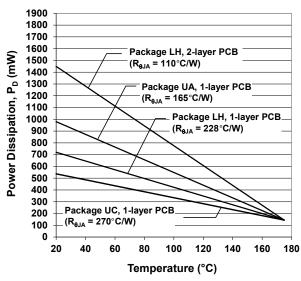

|                                       | I <sub>CC(L1)</sub>    | $I_{CC(L1)}$ is the default $I_{CC(L)}$ current                                             |                    | 5       | -                   | 6.9  | mA    |

|                                       | I <sub>CC(L2)</sub>    |                                                                                             |                    | 2       | -                   | 5    | mA    |

| Supply Current                        | I <sub>CC(H)</sub>     |                                                                                             |                    |         | -                   | 17   | mA    |

|                                       | I <sub>SAFE</sub>      | Safe current state; indicates overtemperature or<br>EEPROM error                            |                    | _       | -                   | 1.8  | mA    |

|                                       |                        | No bypass capacitor; C <sub>L</sub> <sup>[5]</sup> = 20 pF                                  | LH and UA          | _       | 50                  | _    | mA/µs |

| Output Slew Rate                      | dI/dt                  | C <sub>BYP</sub> = 100 nF; C <sub>L</sub> <sup>[5]</sup> = 20 pF                            | packages _         |         | 0.22                | _    | mA/µs |

|                                       |                        | Internal bypass capacitor; C <sub>L</sub> <sup>[5]</sup> = 20 pF                            | UC package         | _       | 0.22                | _    | mA/µs |

| Power-On Time [6]                     | t <sub>PO</sub>        | $V_{CC} \ge V_{CC}(min), B > B_{OP}(max), B < B_{RP}(max)$                                  | in)                | _       | _                   | 70   | μs    |

| Power-On State [7]                    | POS                    | $t < t_{PO}, V_{CC} \ge V_{CC(UV)EN}$                                                       |                    |         | I <sub>CC(H)</sub>  |      | mA    |

| Chopping Frequency                    | f <sub>C</sub>         |                                                                                             |                    | _       | 800                 | _    | kHz   |

| Output Jitter (p-p)                   |                        | 1 kHz square wave signal                                                                    |                    | _       | 5                   | _    | μs    |

| ON-BOARD PROTECTION                   |                        |                                                                                             |                    |         |                     |      |       |

| Supply Zener Clamp Voltage            | Vz                     | $I_{CC} = I_{CC(H)} + 1 \text{ mA}, T_A = 25^{\circ}C$                                      |                    | 40      | _                   | _    | V     |

| Reverse Supply Zener Clamp<br>Voltage | V <sub>RZ</sub>        | $I_{CC} = -1 \text{ mA}$                                                                    |                    | _       | -                   | -23  | V     |

| Overtemperature Shutdown              | T <sub>SD</sub>        | Temperature increasing                                                                      |                    | _       | 205                 | _    | °C    |

| Overtemperature Hysteresis            | T <sub>JHYS</sub>      |                                                                                             |                    | _       | 25                  | _    | °C    |

<sup>[3]</sup> Typical data is at  $T_A = 25^{\circ}$ C and  $V_{CC} = 12$  V unless otherwise noted; for design information only. <sup>[4]</sup> UC minimum  $V_{CC}$  is higher to accommodate voltage drop in the internal series resistor. UC package minimum  $V_{CC}$  is higher to accommodate voltage drop in the internal series resistor. This also affects the V<sub>CC(UV)</sub>.

<sup>[5]</sup> C<sub>L</sub> – scope capacitance.

<sup>[6]</sup> Measured from  $V_{CC} \ge V_{CC}$ (min) to valid output. <sup>[7]</sup> Power-on state is defined only when the  $V_{CC}$  slew rate is 1 V/s or greater.

## Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

# **MAGNETIC CHARACTERISTICS:** Valid over full operating voltage and ambient temperature ranges for $T_J < T_J(max)$ and $C_{BYP} = 0.01 \ \mu\text{F}$ , unless otherwise specified

| Characteristics                                 | Symbol                   | Test Conditions                                                                                              | Min. | Typ. <sup>[9]</sup> | Max. | Unit [10] |

|-------------------------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|------|---------------------|------|-----------|

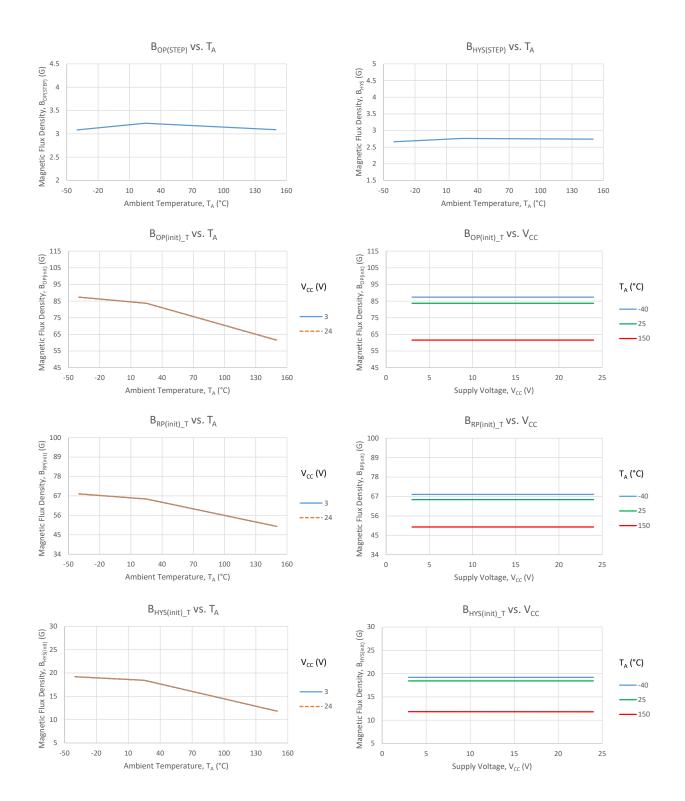

| Initial Operate Point                           | B <sub>OP(init)</sub>    | T <sub>A</sub> = 25°C                                                                                        | 60   | 80                  | 100  | G         |

| Programmable Magnetic                           |                          | Switch Mode, T <sub>A</sub> = 25°C; 8 bits                                                                   | ±10  | -                   | ±600 | G         |

| Operating Point                                 | B <sub>OP(range)</sub>   | Latch Mode, T <sub>A</sub> = 25°C; 8 bits                                                                    | ±20  | -                   | ±600 | G         |

| Average Magnetic Step Size [11]                 | B <sub>OP(STEP)</sub>    | T <sub>A</sub> = 25°C                                                                                        | 2    | 3                   | 4.5  | G         |

| Initial Hysteresis                              | B <sub>HYS(init)</sub>   | T <sub>A</sub> = 25°C                                                                                        | 5    | 15                  | 30   | G         |

| Average Hysteresis<br>Step Size <sup>[12]</sup> | B <sub>HYS(STEP)</sub>   | T <sub>A</sub> = 25°C                                                                                        | 1.5  | 3                   | 5    | G         |

| Programmable Hysteresis in<br>Switch Mode       | B <sub>HYS(range)</sub>  | $T_A = 25^{\circ}C$ ; 5 bits. Switch mode only. In latch mode, hysteresis is 2 × $B_{OP}$                    | 15   | -                   | 70   | G         |

| Initial Release Point                           | B <sub>RP(init)</sub>    | T <sub>A</sub> = 25°C                                                                                        | 45   | -                   | 85   | G         |

|                                                 |                          | 00: Flat                                                                                                     | _    | 0                   | _    | %/°C      |

| Switch Point Temperature                        | TCSEL                    | 01: SmCo                                                                                                     | _    | -0.035              | _    | %/°C      |

| Coefficient                                     | TUSEL                    | 10: NdFeB                                                                                                    | _    | -0.12               | _    | %/°C      |

|                                                 |                          | 11: Ferrite. This is the default value.                                                                      | _    | -0.2                | _    | %/°C      |

| Initial Operate Point Over                      | Р                        | $T_A = -40$ °C; default programming, ferrite temperature coefficient                                         | 65   | -                   | 113  | G         |

| Temperature                                     | B <sub>OP(init)_T</sub>  | $T_A = 150$ °C; default programming, ferrite temperature coefficient                                         | 49   | -                   | 80   | G         |

| Initial Release Point Over                      | D                        | $T_A = -40$ °C; default programming: $B_{OP(init)} = 80$ G (typ) at 25°C and ferrite temperature coefficient | 51   | -                   | 98   | G         |

| Temperature B <sub>RP(init)</sub>               |                          | $T_A$ = 150°C; default programming: $B_{OP(init)}$ = 80 G (typ) at 25°C and ferrite temperature coefficient  | 36   | -                   | 72   | G         |

| Initial Hysteresis Over                         | P                        | $T_A = -40$ °C; default programming, ferrite temperature coefficient                                         | 5    | -                   | 30   | G         |

| Temperature                                     | B <sub>HYS(init)_T</sub> | $T_A = 150$ °C; default programming, ferrite temperature coefficient                                         | 5    | -                   | 30   | G         |

<sup>[9]</sup> Typical data is at  $T_A = 25^{\circ}C$  and  $V_{CC} = 12$  V, unless otherwise noted; for design information only.

<sup>[10]</sup> Magnetic flux density, B, is indicated as a negative value for north-polarity magnetic fields, and a positive value for south-polarity magnetic fields. <sup>[11]</sup> B<sub>OP(STEP)</sub> is a calculated average from the cumulative programmed bits.

$^{[12]}B_{HYS(STEP)}$  is a calculated average from the cumulative programmed bits.

# Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

**PROGRAMMING CHARACTERISTICS:** Valid over full operating voltage and ambient temperature ranges for  $T_J < T_J(max)$  and  $C_{BYP} = 0.01 \ \mu\text{F}$ , unless otherwise specified

| Characteristics                          | Symbol |                                                                       | Tes                                                                                         | st Conditions                                   | Min. | Тур. | Max. | Unit |

|------------------------------------------|--------|-----------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------|------|------|------|------|

| Switch Point Magnitude<br>Selection Bits | BOPSEL |                                                                       |                                                                                             |                                                 | _    | 8    | -    | bit  |

| Magnetic Polarity Bits                   | BOPPOL | The default                                                           | value is 0 fo                                                                               | or south polarity.                              | _    | 1    | -    | bit  |

| Unipolar/Omnipolar                       |        |                                                                       | configure whe                                                                               | ether the device operates like a itch or latch. |      |      |      |      |

| Selection Bit                            | UNI    | E                                                                     | Bit                                                                                         | Description                                     | _    | 1    | _    | bit  |

|                                          |        | UNI                                                                   | LATCH                                                                                       |                                                 |      |      |      |      |

|                                          |        | 0                                                                     | Х                                                                                           | Omnipolar Switch                                |      |      |      |      |

| Switch/Latch Selection Bit               | LATCH  | 1                                                                     | 0                                                                                           | Unipolar Switch (default setting)               | -    | 1    | -    | bit  |

|                                          |        | 1                                                                     | 1                                                                                           | Latch                                           |      |      |      |      |

| Magnetic Hysteresis                      | HYS    | · · · ·                                                               | If configured as a latch, this selection is ignored and the hysteresis is 2 × BOPSEL        |                                                 | _    | 5    | -    | bit  |

| Output Current Level Selection           | ICCL   |                                                                       | If this bit = 0, ICCL = ICCL1. This is the default value.<br>If this bit = 1, ICCL = ICCL2. |                                                 | _    | 1    | _    | bit  |

| Temperature Coefficient                  | TCSEL  | The default                                                           | The default value is 11 for Ferrite temperature coefficient.                                |                                                 | -    | 2    | -    | bit  |

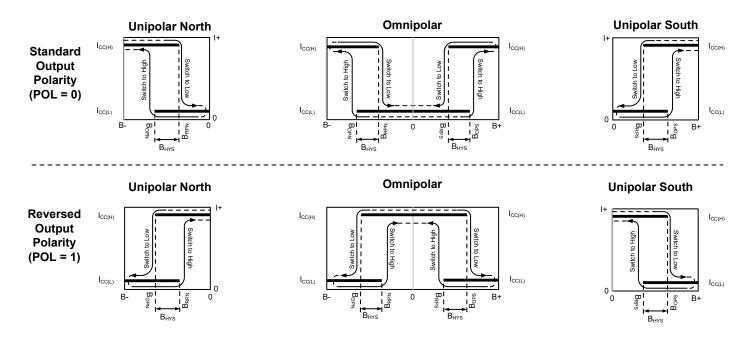

| Output Polarity Bits                     | POL    | The default value is 0 for Standard output polarity.<br>See Figure 1. |                                                                                             | _                                               | 1    | -    | bit  |      |

| Customer ID                              | CUSTID | The default value is 0.                                               |                                                                                             | _                                               | 10   | -    | bit  |      |

| Device Lock Bits                         | LOCK   | The default                                                           | value is 0.                                                                                 |                                                 | _    | 1    | _    | bit  |

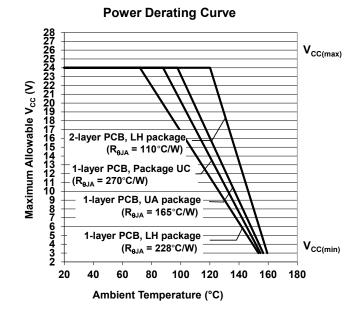

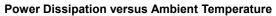

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol           | Dol Test Conditions*                                                            |     |      |  |

|----------------------------|------------------|---------------------------------------------------------------------------------|-----|------|--|

| Package Thermal Resistance |                  | Package LH, on 1-layer PCB based on JEDEC standard                              | 228 | °C/W |  |

|                            | D                | Package LH, on 2-layer PCB with 0.463 in. <sup>2</sup> of copper area each side | 110 | °C/W |  |

|                            | R <sub>0JA</sub> | Package UA, on 1-layer PCB with copper limited to solder pads                   | 165 | °C/W |  |

|                            |                  | Package UC, on 1-layer PCB with copper limited to solder pads                   | 270 | °C/W |  |

\*Additional thermal information available on the Allegro website.

#### CHARACTERISTIC PERFORMANCE DATA

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

# Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

#### FUNCTIONAL DESCRIPTION

#### **Functional Safety**

The APS11900 was designed in accordance with the international standard for automotive functional safety, ISO 26262. This

product achieves an ASIL (Automotive Safety Integrity Level) rating of ASIL A according to the standard. The APS11900 is classified as a SEooC (Safety Element out of Context) and can be easily integrated into safety-critical systems requiring higher ASIL ratings that incorporate

external diagnostics or use measures such as redundancy. Safety documentation will be provided to support and guide the integration process. Contact your local FAE for A<sup>2</sup>-SIL<sup>TM</sup> documentation: www.allegromicro.com/ASIL.

The APS11900 has internal diagnostics to check the voltage supply (an undervoltage lockout regulator) and to detect overtemperature conditions. See the Diagnostics section for more information.

#### Operation

The APS11900 devices are two-wire EEPROM-based fieldprogrammable planar Hall-effect devices. The user can select whether the device should respond to a north or south magnetic field (unipolar) or both (bipolar or omnipolar). There is a choice of two output current levels,  $I_{CC(L1)}$  and  $I_{CC(L2)}$ , and the user can determine which output state applies,  $I_{CC(L)}$  or  $I_{CC(H)}$ , when the magnetic field is present.

The difference between the magnetic operate and release points is the hysteresis,  $B_{\rm HYS}$ . Hysteresis allows clean switching of the output even in the presence of external mechanical vibration and electrical noise. The user can program the desired hysteresis level when configured as a switch. When configured as a latch, the hysteresis is automatically set to double the programmed operating point,  $B_{\rm OP}$ .

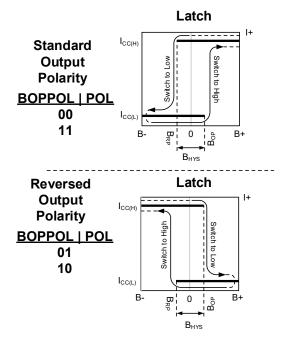

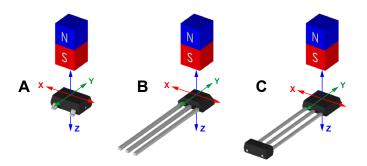

Figure 1 shows the potential unipolar and omnipolar configuration options for the APS11900 when used as a switch. Figure 2 shows the output options when configured as a latch. The direction of the applied magnetic field is perpendicular to the branded face of the APS11900. See Figure 3 for an illustration.

Figure 1: Hall Switch Magnetic and Output Current Polarity Options B- indicates increasing north polarity magnetic field strength, and B+ indicates increasing south polarity magnetic field strength.

Allegro MicroSystems 955 Perimeter Road Manchester, NH 03103-3353 U.S.A. www.allegromicro.com

# Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

Figure 2: Hall Latch Magnetic and Output Current Polarity Options B- indicates increasing north polarity magnetic field strength, and B+ indicates increasing south polarity magnetic field strength.

Figure 3: Magnetic Sensing Orientations APS11900 LH (Panel A), UA (Panel B), and UC (Panel C)

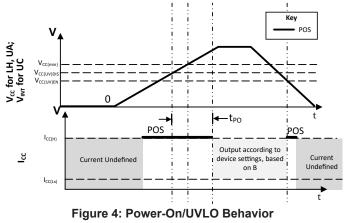

### **Power-On Behavior**

The APS11900 has an internal voltage regulator with undervoltage lockout. As the device powers up, it stays in the power-on state (POS) of  $I_{CC(H)}$  until the supply voltage exceeds  $V_{CC(UV)DIS}$ . Then the device reads the device configuration registers from EEPROM and checks that the EEPROM values are valid by comparing the calculated Error Correction Code (ECC) for each register against the stored ECC. After t<sub>PO</sub>, the current consumption is  $I_{CC(L)}$  or  $I_{CC(H)}$ , according to the magnetic field and the device configuration, as shown in Figure 1 and Figure 2.

Similarly, when the supply voltage decreases, the device returns to the power-on state (POS) when the supply voltage drops below  $V_{CC(UV)EN}$ , as shown in Figure 4.

When the device powers on in the hysteresis range (less than  $B_{OP}$  and higher than  $B_{RP}$ ), the output corresponds to the power-on state. In this case, the correct state is attained after the first excursion beyond  $B_{OP}$  or  $B_{RP}$ .

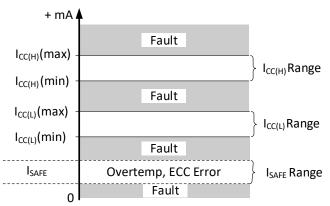

### **Diagnostic Features**

When properly supplied, APS11900 always has current flowing at a specified level: either  $I_{CC(H)}$ ,  $I_{CC(L)}$ , or  $I_{SAFE}$ . Any current outside of these narrow ranges is a fault condition. If there is a short, current increases so that  $I_{CC} > I_{CC(H)}$  (max), outside the valid  $I_{CC(H)}$  range. If there is an open, the current lowers below the  $I_{CC(L)}$  (min), outside the valid output current range. In this way, connectivity issues between the ECU and the sensor can easily be detected.

Additionally, the APS11900 has an overtemperature feature: if the junction temperature increases beyond  $T_{JF}$ , the current is reduced to  $I_{SAFE}$ . The device current also changes to  $I_{SAFE}$  if there is an error in the EEPROM ECC, which is checked at power-on and

after an overtemperature event. There is a LOCK bit that should be set once end-of-line programming has been completed. Setting the LOCK bit prevents any change in device configuration in the field.

Any value of  $I_{\rm CC}$  between the allowed ranges for  $I_{\rm CC(H)}$  and  $I_{\rm CC(L)}$  indicates a general fault condition.

Figure 5: Interpreting I<sub>CC</sub> for System-Level Diagnostics

### **Temperature Coefficient and Magnet Selection**

The APS11900 allows the user to select the magnetic temperature coefficient to compensate for drifts of SmCo, NdFeB, and ferrite magnets over temperature—as indicated in the specifications table on page 5. This compensation improves the magnetic system performance over the entire temperature range. For example, the magnetic field strength from ferrite decreases as the temperature increases from  $25^{\circ}$ C to  $150^{\circ}$ C. This lower magnetic field strength means that a lower switching threshold is required to maintain switching at the same distance from the magnet to the sensor. Correspondingly, higher switching thresholds are required at cold temperatures, as low as  $-40^{\circ}$ C, due to the higher magnetic field strength from the ferrite magnet.

For example, the typical ferrite compensation is  $-0.2\%^{\circ}$ C. With a 25°C temperature B<sub>OP</sub> switch point of 80 G, the switch point changes nominally by  $-0.2\%^{\circ}$ C × 80 × (150°C  $-25^{\circ}$ C) = -20 G to 80 G -20 G = 60 G at 150°C. And at  $-40^{\circ}$ C, the switch point changes by  $-0.2\%^{\circ}$ C × 80 × ( $-40^{\circ}$ C  $-25^{\circ}$ C) = 10 G to 80 G + 10 G = 90 G. The APS11900 compensate the switching thresholds over temperature as described above. It is recommended that system designers evaluate their magnetic circuit over the expected operating temperature range to ensure the magnetic switching requirements are met.

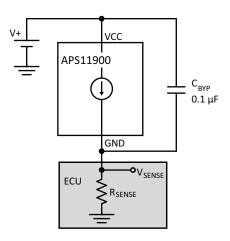

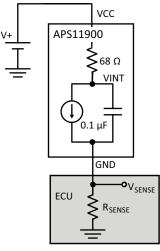

### Applications

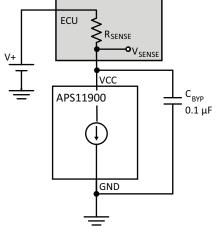

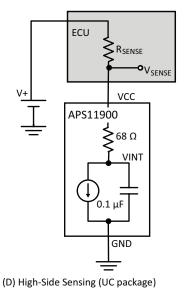

For the LH and UA packages, an external bypass capacitor (from 0.01  $\mu$ F to 0.1  $\mu$ F) should be connected (in close proximity to the Hall element) between the supply and ground of the device to reduce both external noise and noise generated by the chopper stabilization. Some applications may require additional EMC immunity, which is achieved with an enhanced protection circuit. For example, increasing the bypass capacitor from 0.01  $\mu$ F to 0.1  $\mu$ F improves immunity to Powered ESD (ISO 10605) and Direct Capacitive Coupling.

A series resistor and a 0.1  $\mu$ F bypass capacitor are integrated into the UC package, making it easy to achieve an EMC-robust design with no external components or PCB required.

Note that the bypass capacitor selection directly affects the slew rate. See the Electrical Characteristics table for the typical slew rate with 0.1  $\mu$ F bypass capacitor. A 0.01  $\mu$ F bypass capacitor slew rate is 10 times faster. Typical application circuits are shown in "Figure 6: Typical Application Circuits" on page 14.

Extensive applications information for Hall-effect devices is available in:

- Hall-Effect IC Applications Guide, AN27701

- Hall-Effect Devices: Guidelines for Designing Subassemblies Using Hall-Effect Devices, AN27703.1

- Soldering Methods for Allegro's Products SMT and Through-Hole, AN26009

- www.allegromicro.com/ASIL

All are provided on the Allegro website:

www.allegromicro.com

# Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

(A) Low-Side Sensing (LH, UA package)

(C) Low-Side Sensing (UC package)

(B) High-Side Sensing (LH, UA package)

**Figure 6: Typical Application Circuits**

#### **Chopper Stabilization Technique**

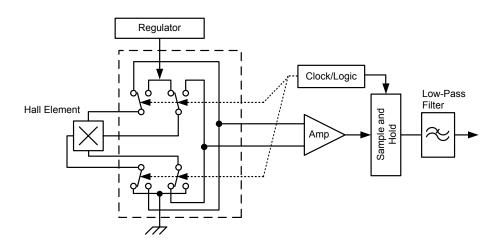

A limiting factor for switch point accuracy when using Halleffect technology is the small-signal voltage developed across the Hall plate. This voltage is proportionally small relative to the offset that can be produced at the output of the Hall sensor. This makes it difficult to process the signal and maintain an accurate, reliable output over the specified temperature and voltage range. Chopper stabilization is a proven approach used to minimize Hall offset.

The technique, dynamic quadrature offset cancellation, removes key sources of the output drift induced by temperature and package stress. This offset reduction technique is based on a signal modulation-demodulation process. "Figure 7: Model of Chopper Stabilization Circuit (Dynamic Offset Cancellation)" illustrates how it is implemented.

The undesired offset signal is separated from the magnetically induced signal in the frequency domain through modulation. The subsequent demodulation acts as a modulation process for the offset, causing the magnetically induced signal to recover its original spectrum at baseband while the DC offset becomes a high-frequency signal. Then, using a low-pass filter, the signal passes while the modulated DC offset is suppressed. Allegro's innovative chopper-stabilization technique uses a high-frequency clock.

The high-frequency operation allows a greater sampling rate that produces higher accuracy, reduced jitter, and faster signal processing. Additionally, filtering is more effective and results in a lower noise analog signal at the sensor output. Devices such as the APS11900 that use this approach have an extremely stable quiescent Hall output voltage, are immune to thermal stress, and have precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process that allows the use of low offset and low noise amplifiers in combination with high-density logic and sample-and-hold circuits.

Figure 7: Model of Chopper Stabilization Circuit (Dynamic Offset Cancellation)

## Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

#### POWER DERATING

The device must be operated below the maximum junction temperature,  $T_J$  (max). Reliable operation may require derating supplied power and/or improving the heat dissipation properties of the application.

Thermal Resistance (junction to ambient),  $R_{\theta JA}$ , is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to ambient air.  $R_{\theta JA}$  is dominated by the Effective Thermal Conductivity, K, of the printed circuit board, which includes adjacent devices and board layout. Thermal resistance from the die junction to case,  $R_{\theta JC}$ , is a relatively small component of  $R_{\theta JA}$ . Ambient air temperature,  $T_A$ , and air motion are significant external factors in determining a reliable thermal operating point.

The following three equations can be used to determine operation points for given power and thermal conditions.

$$P_D = V_{IN} \times I_{IN} \tag{1}$$

$$\Delta T = P_D \times R_{\theta JA} \tag{2}$$

$$T_J = T_A + \Delta T \tag{3}$$

For example, given common conditions:  $T_A = 25^{\circ}C$ ,  $V_{CC} = 12$  V,  $I_{CC} = 6$  mA, and  $R_{\theta JA} = 110^{\circ}C/W$  for the LH package, then:

$$P_D = V_{CC} \times I_{CC} = 12 \ V \times 6 \ mA = 72 \ mW$$

$$\Delta T = P_D \times R_{\theta JA} = 72 \ mW \times 110^{\circ} C/W = 7.92^{\circ} C$$

$$T_J = T_A + \Delta T = 25^{\circ} C + 7.92^{\circ} C = 32.92^{\circ} C$$

#### Determining Maximum V<sub>CC</sub>

For a given ambient temperature,  $T_A$ , the maximum allowable power dissipation as a function of  $V_{CC}$  can be calculated.  $P_D$  (max) represents the maximum allowable power level without exceeding  $T_J$  (max) at a selected  $R_{\theta JA}$  and  $T_A$ .

Example:  $V_{CC}$  at  $T_A = 150^{\circ}$ C, package UA, using low-K PCB. Using the worst-case ratings for the device, specifically:  $R_{\theta JA} = 165^{\circ}$ C/W,  $T_J$  (max) = 165°C,  $V_{CC}$  (max) = 24 V, and  $I_{CC}$  (max) = 17 mA, calculate the maximum allowable power level,  $P_D$  (max). First, using equation 3:

$$\Delta T (max) = T_I (max) - T_A = 165^{\circ}C - 150^{\circ}C = 15^{\circ}C$$

This provides the allowable increase to  $T_J$  resulting from internal power dissipation. Then, from equation 2:

$$P_D(max) = \Delta T(max) \div R_{\theta JA} = 15^{\circ}C \div 165^{\circ}C/W = 91 \ mW$$

Finally, using equation 1, solve for maximum allowable  $V_{CC}$  for the given conditions:

$$V_{CC}$$

(est) =  $P_D$  (max) ÷  $I_{CC}$  (max) = 91 mW ÷ 17 mA = 5.4 V

The result indicates that, at  $T_A$ , the application and device can dissipate adequate amounts of heat at voltages  $\leq V_{CC}$  (est).

If the application requires  $V_{CC} > V_{CC(est)}$  then  $R_{\theta JA}$  must by improved. This can be accomplished by adjusting the layout, PCB materials, or by controlling the ambient temperature.

#### Determining Maximum T<sub>A</sub>

In cases where the V<sub>CC</sub> (max) level is known, and the system designer would like to determine the maximum allowable ambient temperature T<sub>A</sub> (max), for example, in a worst-case scenario with conditions V<sub>CC</sub> (max) = 24 V, I<sub>CC</sub> (max) = 17 mA, and R<sub> $\theta$ JA</sub> = 228°C/W for the LH package using equation 1, the largest possible amount of dissipated power is:

$$P_D = V_{IN} \times I_{IN}$$

$$P_D = 24 \ V \times 17 \ mA = 408 \ mW$$

Then, by rearranging equation 3 and substituting with equation 2:

$$T_A (max) = T_J (max) - \Delta T$$

$$T_A (max) = 165^{\circ}C - (408 \text{ mW} \times 228^{\circ}C/W)$$

$$T_A (max) = 165^{\circ}C - 93^{\circ}C = 72^{\circ}C$$

Finally, note that the  $T_A$  (max) rating of the device is 150°C and performance is not guaranteed above this temperature for any power level.

## Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

### **PROGRAMMING GUIDELINES**

#### Overview

Programming is accomplished by sending a series of input voltage pulses serially through the VCC (supply) pin of the device. A unique combination of different voltage level pulses controls the internal programming logic of the device to select a desired programmable parameter and change its value. There are three voltage levels that must be taken into account when programming. These levels are referred to as high ( $V_{PH}$ ), mid ( $V_{PM}$ ), and low ( $V_{PL}$ ).

The APS11900 family allows the user to write to volatile configuration registers, called shadow registers, to "try" the configuration. Then the device configuration can be written to EEPROM, nonvolatile memory.

Shadow registers are reset after cycling the supply voltage.

The EEPROM has a limited number of write cycles. For this reason, it is recommended to use the Shadow registers ("Try Mode") to determine the correct device configuration.

After the desired device configuration has been determined, write the values into the device EEPROM and write the lock bit to prevent further access to the EEPROM.

After power-on, the EEPROM registers are read and the values are written into the shadow registers as described in the section "Power-On Behavior" on page 12 of this datasheet.

The following functionality is available through the APS11900 programming interface:

| Function              | Description                                                                                                                                                        |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shadow Register Write | Write volatile configuration registers in "Try Mode".                                                                                                              |

| Shadow Register Read  | Read volatile configuration registers in "Try Mode".                                                                                                               |

| EEPROM Register Write | Write configuration to non-volatile memory<br>(EEPROM). Note that EEPROM has limited write<br>cycles as described in the Absolute Maximum<br>Specifications table. |

| EEPROM Register Read  | Read non-volatile configuration registers (EEPROM).                                                                                                                |

| EEPROM Margining      | Procedure to validate that the EEPROM bank was written successfully.                                                                                               |

| Increment BOP         | This mode allows the user to increment BOPSEL each time a HV pulse is sent.                                                                                        |

| Decrement BOP         | This mode allows the user to decrement BOPSEL each time a HV pulse is sent.                                                                                        |

| Increment BHYS        | This mode allows the user to increment BHYS each time a HV pulse is sent.                                                                                          |

| Decrement BHYS        | This mode allows the user to decrement BHYS each time a HV pulse is sent.                                                                                          |

Although any programmable variable power supply can be used to generate the pulse waveforms, Allegro highly recommends using the Allegro Sensor IC Evaluation Kit, ASEK-20, available through your local Allegro sales representative. The manual for the kit is available for download on the Allegro MicroSystems website.

For detailed programming instructions, refer to the APS11900 Customer EEPROM Programming manual.

# Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

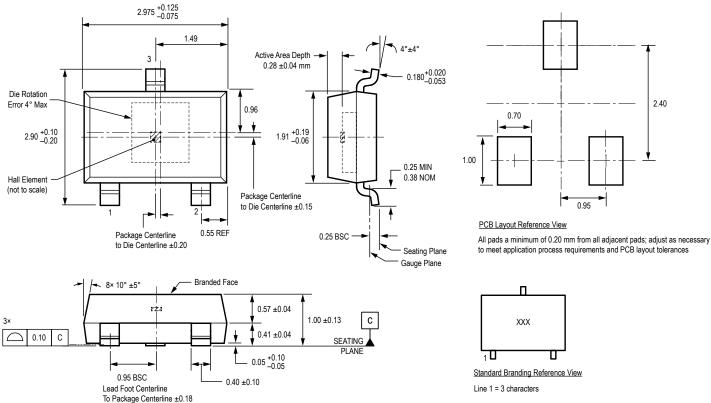

#### Package LH, 3-Pin SOT23W

#### For Reference Only – Not for Tooling Use (Reference Allegro DWG-000628, Rev. 1) NOT TO SCALE Dimensions in millimeters Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

Line 1: Last 3 digits of Part Number

Branding scale and appearance at supplier discretion

## Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

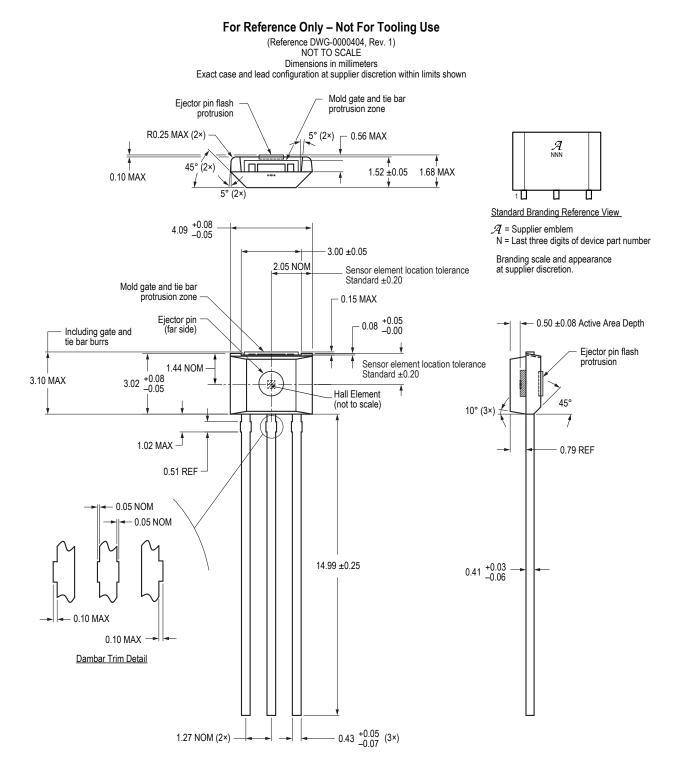

#### Package UA, 3-Pin SIP

# Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

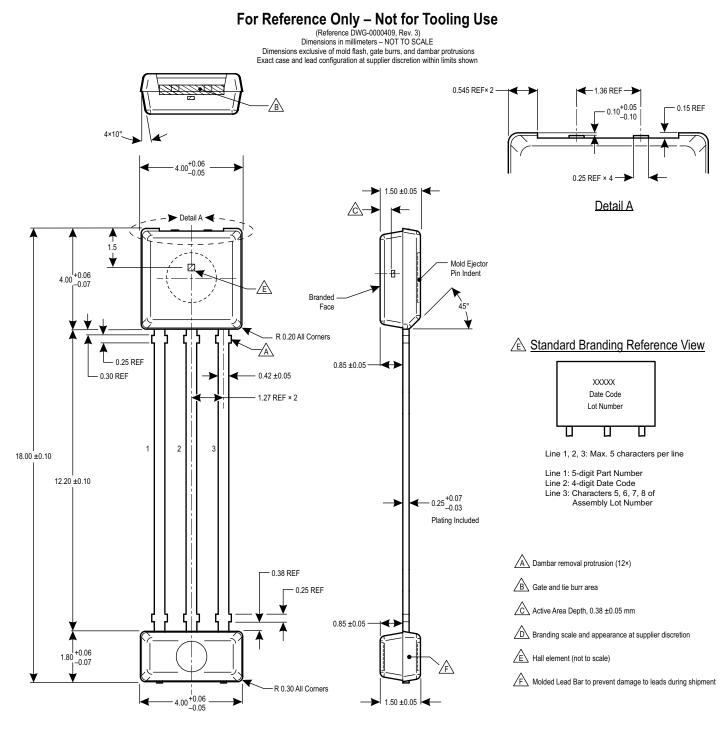

Package UC, 3-Pin SIP

## Two-Wire End-of-Line Programmable Hall-Effect Switch/Latch

#### **REVISION HISTORY**

| Number | Date             | Description                                                                                                                      |

|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------|

| _      | March 23, 2018   | Initial release                                                                                                                  |

| 1      | April 18, 2018   | Corrected supply current values and plots (pages 4 and 8)                                                                        |

| 2      | February 4, 2019 | Minor editorial updates                                                                                                          |

| 3      | April 1, 2019    | Updated ASIL status (pages 1 and 10)                                                                                             |

| 4      | April 20, 2020   | Updated selection guide (page 2) and minor editorial updates                                                                     |

| 5      | August 26, 2020  | Corrected Output Current Selection Level test conditions and added figure note to Output Polarity Bits test conditions (page 6). |

| 6      | October 27, 2021 | Updated package drawings (pages 18-20)                                                                                           |

| 7      | July 21, 2022    | Updated ASIL status (pages 1 and 10) and made minor editorial updates                                                            |

Copyright 2022, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

<u>Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of</u> <u>Allegro's product can reasonably be expected to cause bodily harm.</u>

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com