## FEATURES AND BENEFITS

- ASIL A functional safety compliance

- Planar and vertical Hall-effect sensor ICs

- 3.3 to 24 V operation

- Automotive-grade ruggedness and fault tolerance

- □ Extended AEC-Q100 qualification

- □ Internal protection circuits enable 40 V load dump compliance

- □ Reverse-battery protection

- □ Output short-circuit and overvoltage protection

- □ Operation from -40°C to 175°C junction temperature □ High EMC immunity

- Symmetrical latch switch points

- Choice of output polarity

- Open-drain output

- Solid-state reliability

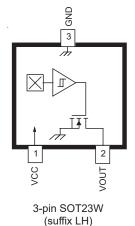

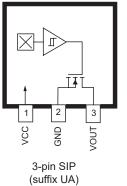

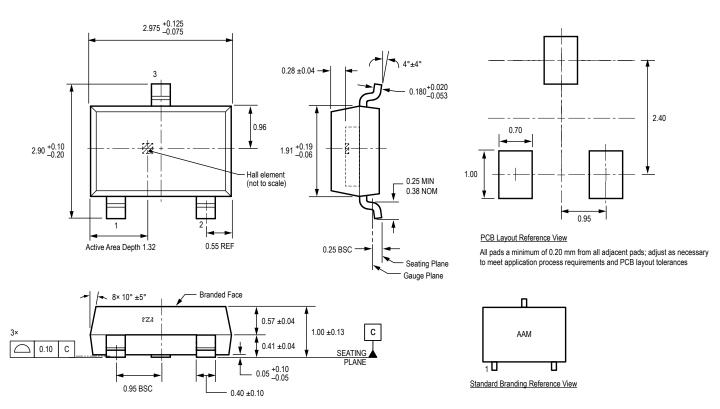

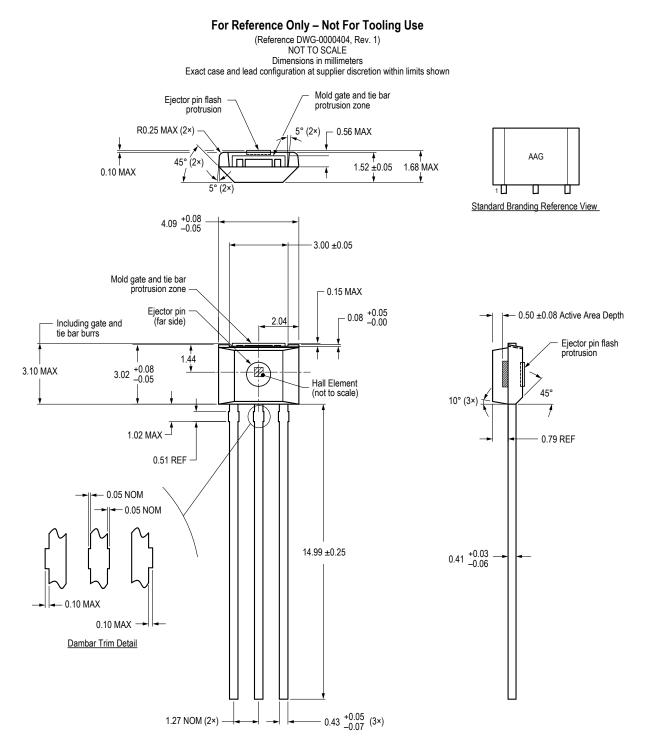

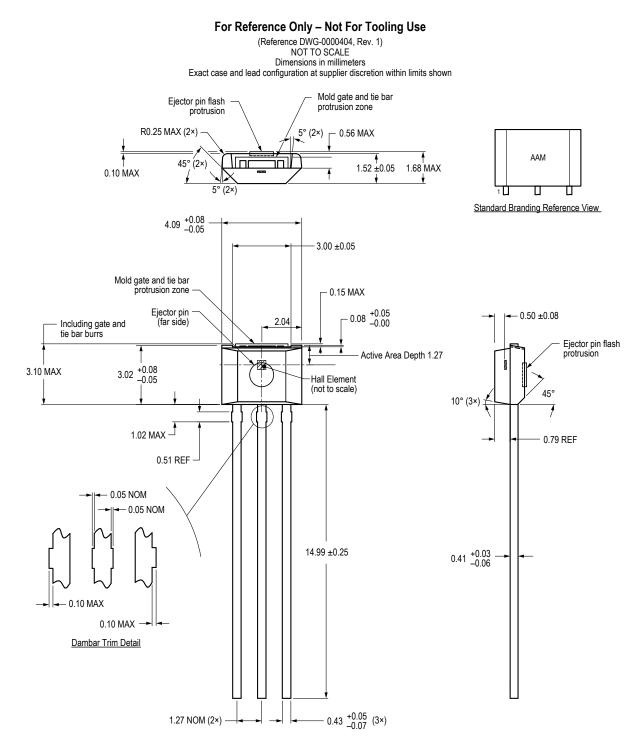

## PACKAGES

Not to scale

3-pin SOT23W (suffix LH)

3-pin SIP (suffix UA)

## DESCRIPTION

The APS12000 and APS12060 families of Hall-effect latches are AEC-Q100 qualified for 24 V automotive applications and compliant with ISO 26262:2011 ASIL A. These sensors are temperature-stable and suited for operation over extended junction temperature ranges up to 175°C. The APS12000 and APS12060 families are available in several different magnetic sensitivities to offer flexible options for system design. They are available in active high and active low variants for ease of integration into electronic subsystems.

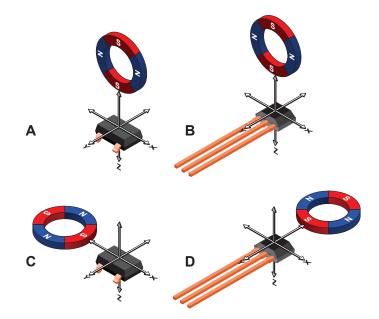

The APS12000 features a Hall-effect element that is sensitive to magnetic flux perpendicular to the face of the IC package. The APS12060 features a vertical Hall-effect sensing element sensitive to magnetic flux parallel to the face of the IC package.

The devices include on-board reverse-battery and overvoltage protection for operating directly from an automobile battery, as well as protection from shorts to ground by limiting the output current until the short is removed. The device is especially suited for operation from unregulated supplies.

Continued on next page ...

#### **TYPICAL APPLICATIONS**

- · Automotive and industrial safety systems

- Industrial motors/encoders

- Trunk/door/liftgate/wiper motors

- Electronic power steering (EPS)

- Transmission actuators

## **DESCRIPTION** (continued)

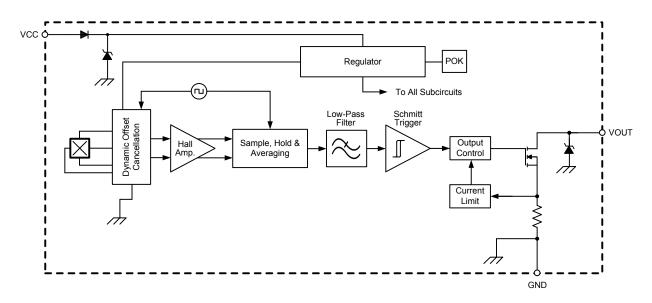

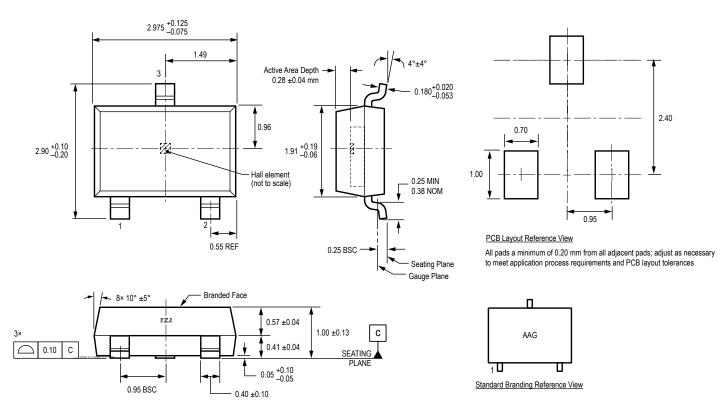

Two package styles provide a choice of through-hole or surface mounting. Package type LH is a modified 3-pin SOT23W surface mount package, while package type UA is a 3-pin ultra-mini SIP for through-hole mounting. Both packages are lead (Pb) free, with 100% matte-tin-plated leadframes.

#### L – -40°C to +150°C

#### **SELECTION GUIDE**

| Part Number <sup>[1]</sup> | Packing <sup>[2]</sup>         | Mounting                   | Sensing<br>Orientation | Output Polarity<br>for B > B <sub>OP</sub> | Typical B <sub>OP</sub> /B <sub>RP</sub><br>Threshold (G) |  |

|----------------------------|--------------------------------|----------------------------|------------------------|--------------------------------------------|-----------------------------------------------------------|--|

| APS12000LLHALT-0H          | 7-in. reel, 3000 pieces/reel   | 3-pin SOT23W surface mount |                        |                                            |                                                           |  |

| APS12000LLHALX-0H          | 13-in. reel, 10000 pieces/reel | 3-pin SOT23W surface mount | Z-Axis                 | High                                       | ±40                                                       |  |

| APS12000LUAA-0H            | Bulk, 500 pieces/bag           | 3-pin SIP through-hole     |                        |                                            |                                                           |  |

| APS12060LLHALT-0L          | 7-in. reel, 3000 pieces/reel   | 3-pin SOT23W surface mount | X Avia                 |                                            |                                                           |  |

| APS12060LLHALX-0L          | 13-in. reel, 10000 pieces/reel | 3-pin SOT23W surface mount | X-Axis                 | Low                                        | ±40                                                       |  |

| APS12060LUAA-0L            | Bulk, 500 pieces/bag           | 3-pin SIP through-hole     | Y-Axis                 |                                            | 1                                                         |  |

| APS12060LLHALT-0H          | 7-in. reel, 3000 pieces/reel   | 3-pin SOT23W surface mount | X-Axis                 | High                                       |                                                           |  |

| APS12060LLHALX-0H          | 13-in. reel, 10000 pieces/reel | 3-pin SOT23W surface mount | A-AXIS                 |                                            | ±40                                                       |  |

| APS12060LUAA-0H            | Bulk, 500 pieces/bag           | 3-pin SIP through-hole     | Y-Axis                 |                                            |                                                           |  |

| APS12060LLHALT-1L          | 7-in. reel, 3000 pieces/reel   | 3-pin SOT23W surface mount | X Avia                 |                                            |                                                           |  |

| APS12060LLHALX-1L          | 13-in. reel, 10000 pieces/reel | 3-pin SOT23W surface mount | X-Axis                 | Low                                        | ±95                                                       |  |

| APS12060LUAA-1L            | Bulk, 500 pieces/bag           | 3-pin SIP through-hole     | Y-Axis                 | 1                                          |                                                           |  |

<sup>[1]</sup> Contact Allegro MicroSystems for options not listed in the selection guide.

<sup>[2]</sup> Contact Allegro MicroSystems for additional packing options.

#### **ABSOLUTE MAXIMUM RATINGS**

| Characteristic                       | Symbol              | Notes          | Rating     | Units |

|--------------------------------------|---------------------|----------------|------------|-------|

| Supply Voltage <sup>[1]</sup>        | V <sub>CC</sub>     |                | 40         | V     |

| Reverse Supply Voltage [1]           | V <sub>RCC</sub>    |                | -18        | V     |

| Output Voltage <sup>[1]</sup>        | V <sub>OUT</sub>    |                | -0.3 to 32 | V     |

| Output Current <sup>[2]</sup>        | I <sub>OUT</sub>    |                | 40         | mA    |

| Reverse Output Current               | I <sub>ROUT</sub>   |                | -50        | mA    |

| Magnetic Flux Density <sup>[3]</sup> | В                   |                | Unlimited  | G     |

| Operating Ambient Temperature        | T <sub>A</sub>      | Range L        | -40 to 150 | °C    |

| Maximum Junction Temperature         | т                   |                | 165        | °C    |

| Maximum Junction Temperature         | T <sub>J(max)</sub> | For 1000 hours | 175        | °C    |

| Storage Temperature                  | T <sub>stg</sub>    |                | -65 to 170 | °C    |

<sup>[1]</sup> This rating does not apply to extremely short voltage transients. Transient events such as Load Dump and/or ESD have individual, specific ratings. <sup>[2]</sup> Through short-circuit current limiting device.

<sup>[3]</sup> Guaranteed by design.

#### ESD PERFORMANCE<sup>[4]</sup>

| Characteristic | Symbol                | Notes                                      | Rating | Units |

|----------------|-----------------------|--------------------------------------------|--------|-------|

| ESD Voltage    | V <sub>ESD(HBM)</sub> | Human Body Model according to AEC-Q100-002 | ±11    | kV    |

<sup>[4]</sup> ESD ratings provided are based on qualification per AEC-Q100 as an expected level of ESD robustness.

#### PINOUT DIAGRAMS AND TERMINAL LIST (View from branded face)

#### **Terminal List**

| Name | Description                    | Number |    |  |

|------|--------------------------------|--------|----|--|

| Name | Description                    | LH     | UA |  |

| VCC  | Connects power supply to chip  | 1      | 1  |  |

| VOUT | Output from circuit            | 2      | 3  |  |

| GND  | Terminal for ground connection | 3      | 2  |  |

# **APS12000 and APS12060**

# **Vertical and Planar Hall-Effect Latches**

### **ELECTRICAL CHARACTERISTICS:** Valid over full operating voltage and ambient temperature ranges for $T_J < T_{J(max)}$ and

$C_{BVP} = 0.1 \,\mu$ F, unless otherwise specified

| Characteristics                                    | Symbol                | Test Conditions                                                                                             | Min. | Typ. <sup>[1]</sup> | Max. | Unit |

|----------------------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------|------|---------------------|------|------|

| SUPPLY AND STARTUP                                 |                       | · · · · · ·                                                                                                 |      |                     |      |      |

| Supply Voltage                                     | V <sub>CC</sub>       |                                                                                                             | 3.3  | _                   | 24   | V    |

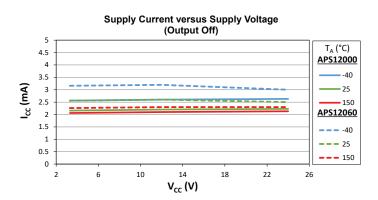

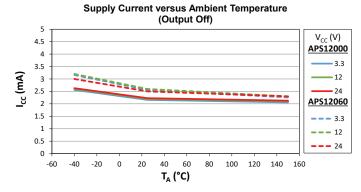

| Querry has Querry to                               |                       | APS12000                                                                                                    | 1    | 2.2                 | 4    | mA   |

| Supply Current                                     | Icc                   | APS12060                                                                                                    | 1    | 2.5                 | 5    | mA   |

| Power-On Time <sup>[2]</sup>                       | t <sub>PO</sub>       | $V_{CC} \ge V_{CC}(min)$                                                                                    | _    | 180                 | 350  | μs   |

| Power-On State <sup>[5]</sup>                      | POS                   | $V_{CC} \ge V_{CC}(min), t < t_{PO}$                                                                        |      | High                |      | _    |

| Undervoltage Lockout <sup>[3]</sup>                | V <sub>UVLO</sub>     | Voltage threshold at which the device is fully disabled during power down                                   | _    | 2.25                | _    | V    |

| UVLO Reset Time <sup>[3]</sup>                     | t <sub>POR</sub>      |                                                                                                             | _    | 100                 | _    | μs   |

| CHOPPER STABILIZATION AND OUT                      | PUT MOSF              | ET CHARACTERISTICS                                                                                          |      |                     |      |      |

| Chopping Frequency                                 | f <sub>C</sub>        |                                                                                                             | _    | 800                 | _    | kHz  |

| Output Leakage Current <sup>[4]</sup>              | I <sub>OUTOFF</sub>   | $V_{OUT(OFF)}$ = 12 V, $T_A$ = -40°C to 85°C, output off,<br>$V_{CC} \ge V_{CC(min)}$ , t > t <sub>PO</sub> | _    | -                   | 0.1  | μA   |

| Output Leakage Current                             | IOUTOFF               | $V_{OUT(OFF)} = 24$ V, output off, $V_{CC} \ge V_{CC(min)}$ , $t > t_{PO}$                                  | _    | -                   | 1    | μA   |

| Output Leakage Current, Power-On <sup>[4][5]</sup> | IOUTOFF(PO)           | $V_{CC} \ge V_{CC(min)}, t < t_{PO}$                                                                        | _    | -                   | 95   | μA   |

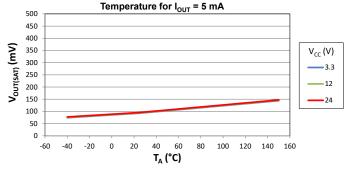

| Output Saturation Voltage                          | V <sub>OUT(SAT)</sub> | Output on, I <sub>OUT</sub> = 5 mA                                                                          | _    | 100                 | 500  | mV   |

| Output Off Voltage                                 | V <sub>OUT(OFF)</sub> |                                                                                                             | _    | -                   | 24   | V    |

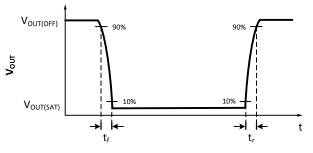

| Output Rise Time <sup>[6][7]</sup>                 | t <sub>r</sub>        | C <sub>L</sub> = 20 pF, R <sub>PULL-UP</sub> = 4.8 kΩ                                                       | _    | 0.2                 | 2    | μs   |

| Output Fall Time <sup>[6][7]</sup>                 | t <sub>f</sub>        | C <sub>L</sub> = 20 pF, R <sub>PULL-UP</sub> = 4.8 kΩ                                                       | _    | 0.1                 | 2    | μs   |

| ON-BOARD PROTECTION                                |                       | · · · · · · · · · · · · · · · · · · ·                                                                       |      |                     |      |      |

| Output Short-Circuit Current Limit                 | I <sub>OM</sub>       | Output on, $V_{PULL-UP} \le 24 V$                                                                           | 15   | 25                  | 40   | mA   |

| Output Zener Clamp Voltage                         | V <sub>Z(OUT)</sub>   | I <sub>OUT</sub> = 1.5 mA, T <sub>A</sub> = 25°C                                                            | 32   | _                   | _    | V    |

| Supply Zener Clamp Voltage                         | Vz                    | $I_{CC} = I_{CC}(max) + 3 \text{ mA}, T_A = 25^{\circ}C$                                                    | 40   | _                   | _    | V    |

| Reverse Battery Zener Clamp Voltage                | V <sub>RZ</sub>       | I <sub>CC</sub> = –5 mA, T <sub>A</sub> = 25°C                                                              | _    | _                   | -18  | V    |

| Reverse Battery Current                            | I <sub>RCC</sub>      | $V_{CC} = -18 \text{ V}, T_A = 25^{\circ}\text{C}$                                                          | -5   | _                   | _    | mA   |

<sup>[1]</sup> Typical data is at  $T_A = 25^{\circ}C$  and  $V_{CC} = 12 V$  unless otherwise noted. <sup>[2]</sup> Measured from  $V_{CC} \ge 3.3 V$  to valid output. <sup>[3]</sup> See Undervoltage Lockout section for operational characteristics.

<sup>[4]</sup> Guaranteed by device design and characterization.

<sup>[5]</sup> See Power-On Behavior section and Figure 4.

<sup>[6]</sup>  $C_L$  = oscilloscope probe capacitance.

<sup>[7]</sup> See Figure 2 - Definition of Output Rise and Fall Time.

Figure 2: Definition of Output Rise and Fall Time

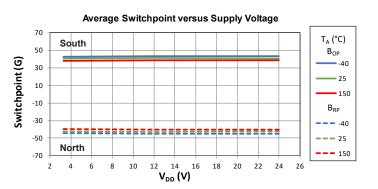

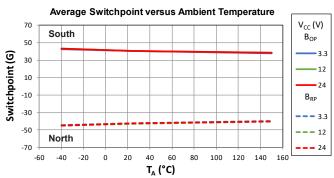

## **MAGNETIC CHARACTERISTICS:** Valid over full operating voltage and ambient temperature ranges for $T_J < T_{J(max)}$ and

$C_{BVP} = 0.1 \,\mu$ F, unless otherwise specified

| Characteristics | Symbol           | Test Conditions | Min.      | Typ. <sup>[1]</sup> | Max. | Unit <sup>[2]</sup> |

|-----------------|------------------|-----------------|-----------|---------------------|------|---------------------|

| -0x OPTION      |                  | ·               | · · · · · |                     |      |                     |

| Operate Point   | B <sub>OPS</sub> | -0x             | 10        | 35                  | 70   | G                   |

| Release Point   | B <sub>RPS</sub> | -0x             | -70       | -35                 | -10  | G                   |

| Hysteresis      | B <sub>HYS</sub> | -0x             | 20        | 70                  | 140  | G                   |

| -1x OPTION      |                  |                 | ,         |                     |      |                     |

| Operate Point   | B <sub>OPS</sub> | -1x Option      | 50        | 95                  | 135  | G                   |

| Release Point   | B <sub>RPS</sub> | -1x Option      | -135      | -95                 | -50  | G                   |

| Hysteresis      | B <sub>HYS</sub> | -1x Option      | 100       | 190                 | 270  | G                   |

| -2x OPTION      | · · · ·          | ·               | · · · · · |                     |      |                     |

| Operate Point   | B <sub>OPN</sub> | -2x Option      | 120       | 150                 | 200  | G                   |

| Release Point   | B <sub>RPN</sub> | -2x Option      | -200      | -150                | -120 | G                   |

| Hysteresis      | B <sub>HYS</sub> | -2x Option      | 140       | 300                 | 400  | G                   |

| -3x OPTION      |                  |                 |           |                     |      |                     |

| Operate Point   | B <sub>OPN</sub> | -3x Option      | 205       | 280                 | 355  | G                   |

| Release Point   | B <sub>RPN</sub> | -3x Option      | -355      | -280                | -205 | G                   |

| Hysteresis      | B <sub>HYS</sub> | -3x Option      | 410       | 560                 | 710  | G                   |

<sup>[1]</sup> Typical data are at  $T_A = 25^{\circ}$ C and  $V_{CC} = 12$  V unless otherwise noted. <sup>[2]</sup> Magnetic flux density, B, is indicated as a negative value for north-polarity magnetic fields, and a positive value for south-polarity magnetic fields.

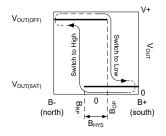

#### **Standard Output Polarity**

**Inverted Output Polarity**

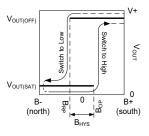

#### Figure 3: Hall Switch Output State vs. Magnetic Field

B- indicates increasing north polarity magnetic field strength, and B+ indicates increasing south polarity magnetic field strength.

# APS12000 and APS12060

# **Vertical and Planar Hall-Effect Latches**

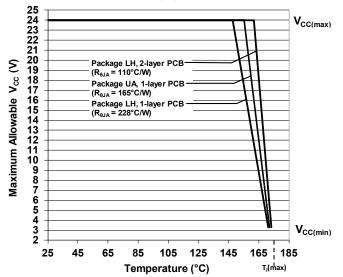

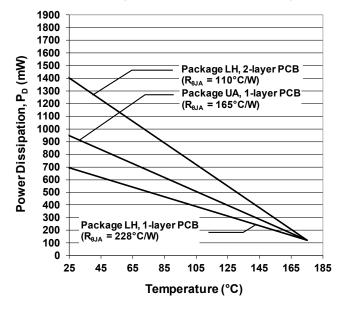

#### PACKAGE THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information.

| Characteristic             | Symbol          | Test Conditions                                                                                       |     | Units |

|----------------------------|-----------------|-------------------------------------------------------------------------------------------------------|-----|-------|

|                            |                 | Package LH, 1-layer PCB with copper limited to solder pads                                            | 228 | °C/W  |

| Package Thermal Resistance | $R_{\theta JA}$ | Package LH, 2-layer PCB with 0.463 in <sup>2</sup> of copper area each side connected by thermal vias |     | °C/W  |

|                            |                 | Package UA, 1-layer PCB with copper limited to solder pads                                            | 165 | °C/W  |

### Power Derating Curve

$T_J(max) = 175^{\circ}C; I_{CC} = I_{CC(max)}, I_{OUT} = 0 \text{ mA (Output Off)}$

#### **Power Dissipation versus Ambient Temperature**

## CHARACTERISTIC PERFORMANCE DATA Electrical Characteristics

#### **Output Saturation Voltage versus Supply Voltage** for I<sub>OUT</sub> = 5 mA 500 450 400 V<sub>OUT(SAT)</sub> (mV) 350 T<sub>A</sub> (°C) 300 -40 250 -25 200 150 150 100 50 0 26 2 6 10 14 18 22 V<sub>cc</sub> (V)

Output Saturation Voltage versus Ambient

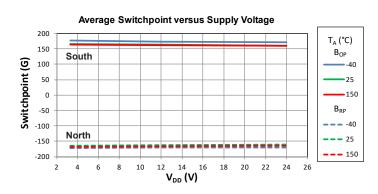

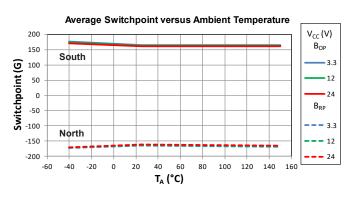

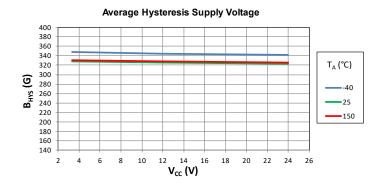

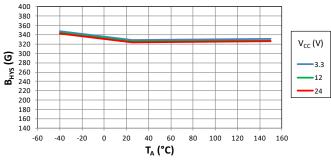

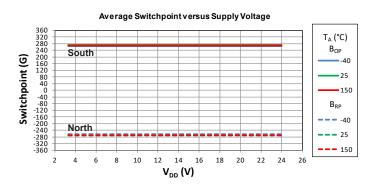

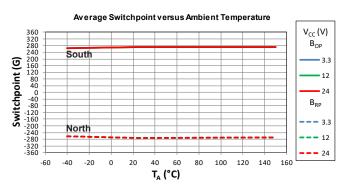

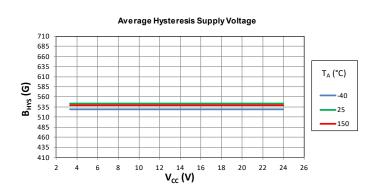

CHARACTERISTIC PERFORMANCE DATA Magnetic Characteristics -0x Option

Average Hysteresis versus Ambient Temperature

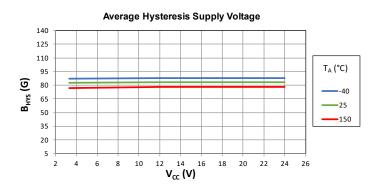

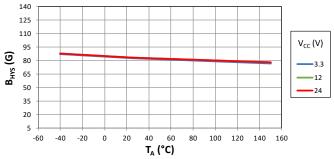

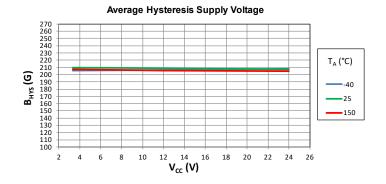

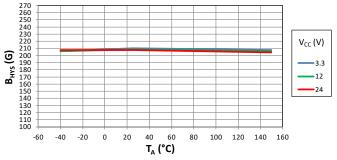

## CHARACTERISTIC PERFORMANCE DATA Magnetic Characteristics -1x Option

Average Hysteresis versus Ambient Temperature

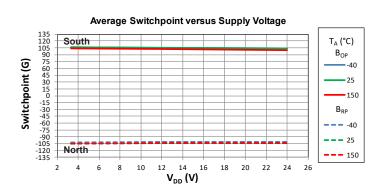

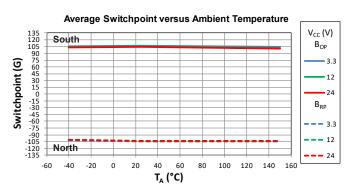

### CHARACTERISTIC PERFORMANCE DATA Magnetic Characteristics -2x Option

Average Hysteresis versus Ambient Temperature

## CHARACTERISTIC PERFORMANCE DATA Magnetic Characteristics -3x Option

Average Hysteresis versus Ambient Temperature

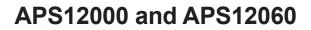

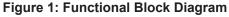

#### FUNCTIONAL DESCRIPTION

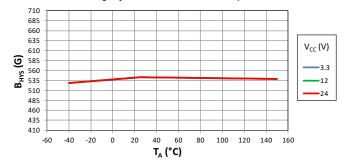

#### **Power-On Behavior**

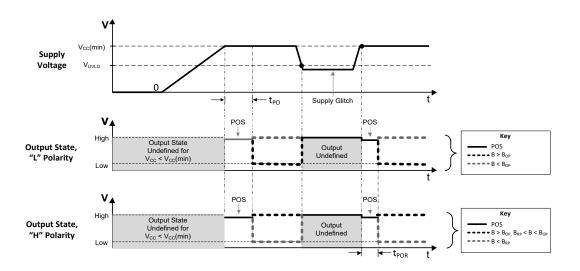

Device power-on begins when the supply voltage reaches  $V_{CC}(min)$ . During the power-on time,  $t_{PO}$ , the device output is off with the exception of the leakage current, I<sub>OUTOFF(PO)</sub>. Use of a large pull-up resistor, R<sub>PULL-UP</sub> (see Figure 6), can influence the Power-On State (POS) voltage level on the output pin during t<sub>ON</sub>. The output voltage level during the POS is a function of the pullup resistor and pull-up voltage. The level can be determined by subtracting the voltage drop created by R<sub>PULL-UP</sub> and I<sub>OUTOFF(PO)</sub> from the pull-up voltage. To retain a power-on output voltage level above V<sub>PULL-UP</sub>/2, a pull-up resistor less than or equal to 20 k $\Omega$  is recommended. After power-on is complete and the power-on time has elapsed, the device output will correspond with the applied magnetic field for  $B > B_{OP}$  and  $B < B_{RP}$ . Powering-on the device in the hysteresis range (less than B<sub>OP</sub> and higher than B<sub>RP</sub>) will cause the device output to remain off. A valid output state is attained after the first excursion beyond B<sub>OP</sub> or B<sub>RP</sub>.

#### **Undervoltage Lockout Operation**

The APS12000 and APS12060 have an internal diagnostic to check the voltage supply (an undervoltage lockout regulator). When the supply voltage falls below the undervoltage lockout voltage threshold,  $V_{UVLO}$ , the device enters reset, where the output state becomes undefined until  $V_{CC}$  is increased to  $V_{CC}$  (min). Once the  $V_{CC}$  (min) threshold is reached, the power-on sequence begins and the output will correspond with the applied magnetic field for  $B > B_{OP}$  and  $B < B_{RP}$  after  $t_{POR}$  has elapsed. In the case the supply voltage does not return to these operational levels, or if the applied magnetic field is within the hysteresis range, the output will remain in the power-on state. See Figure 4 for an example of the undervoltage lockout behavior.

Figure 4: Power-On and Undervoltage Lockout Behavior

## **Functional Safety**

The APS12000 and APS12060 were designed and developed in accordance with the international standard for automotive functional safety, ISO 26262:2011. These products achieve

safety, ISO 26262:2011. These products achieve an ASIL (Automotive Safety Integrity Level) rating of ASIL A according to the standard. The APS12000 and APS12060 are both classified as a SEooC (Safety Element out of Context) and can be easily integrated into safety-critical systems requiring higher ASIL ratings that incorporate external diagnostics or use measures such as redundancy. Safety documentation will be provided to support and guide the integration process. For further information, contact your local FAE for A<sup>2</sup>-SIL<sup>TM</sup> documentation: www. allegromicro.com/ASIL.

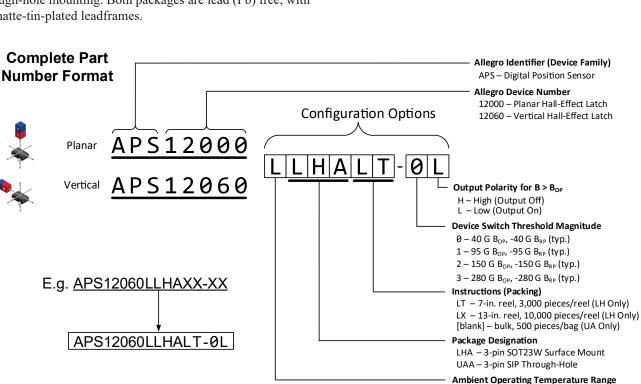

## Operation

The APS12000 and APS12060 are integrated Hall-effect sensor ICs with an open-drain output. The output polarity of the -xL configuration device is Low for a south-polarity magnetic field, B  $> B_{OP}$ , and High for a north polarity magnetic field, B  $< B_{RP}$ . The -xH variant is complementary, in that for this device the output goes High for a south polarity magnetic field, B  $> B_{OP}$ , and Low for a north polarity magnetic field, B  $< B_{RP}$ . The open-drain output is an NMOS transistor that actuates in response to a magnetic field. The direction of the applied magnetic field is perpendicular to the branded face for the APS12000, and parallel with the branded face for the APS12060; see Figure 5 for an illustration. The devices are offered in two packages: the UA package, a 3-pin through-hole mounting configuration, or in the LH package, a 3-pin surface-mount configuration. See the Selection Guide for a complete list of available options.

Figure 5: Magnetic Sensing Orientations APS12000 LH (Panel A), APS12000 UA (Panel B), APS12060 LH (Panel C), and APS12060 UA (Panel D)

## Applications

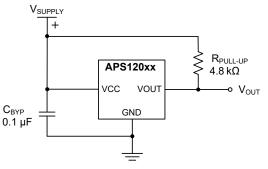

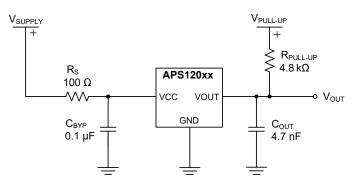

It is strongly recommended that an external bypass capacitor be connected (in close proximity to the Hall element) between the supply and ground of the device to guarantee correct performance under harsh environmental conditions and to reduce noise from internal circuitry. As is shown in Figure 6: Typical and Enhanced Protection Application Circuits, a 0.1  $\mu$ F capacitor is required.

In applications where the APS12000 or APS12060 receives its power from an unregulated source such as a car battery, or where greater immunity is required, additional measures may be employed. Specifications for such transients will vary, so protection circuit design should be optimized for each application. For example, the circuit shown in Figure 6 includes an optional series resistor and output capacitor which improves performance during Powered ESD testing (ISO 10605) and Bulk Current Injection testing (ISO 11452-4). Extensive applications information for Hall-effect devices is available in:

- Hall-Effect IC Applications Guide, AN27701,

- Hall-Effect Devices: Guidelines for Designing Subassemblies Using Hall-Effect Devices AN27703.1

- Soldering Methods for Allegro's Products SMD and Through-Hole, AN26009

- Functional Safety Challenges to the Automotive Supply Chain (https://www.allegromicro.com/en/insights-and-innovations/ technical-documents/general-semiconductor-information/ functional-safety-challenges-automotive-supply-chain)

All are provided on the Allegro website:

www.allegromicro.com

## Typical Applications Circuit

#### Enhanced Protection Circuit

#### Figure 6: Typical and Enhanced Protection Application Circuits

Recommended  $R_{PULL-UP} \le 20 \text{ k}\Omega$ . See Power-On Behavior section.

## Vertical Hall-Effect Sensor Linear Tools

System design and magnetic sensor evaluation often require an indepth look at the overall strength and profile generated by a magnetic field input. To aid in this evaluation, Allegro MicroSystems provides a high-accuracy linear output tool capable of reporting the nonperpendicular magnetic field by means of a vertical Halleffect sensor IC equipped with a calibrated analog output. For further information, contact your local Allegro field applications engineer or sales representative.

# APS12000 and APS12060

# **Vertical and Planar Hall-Effect Latches**

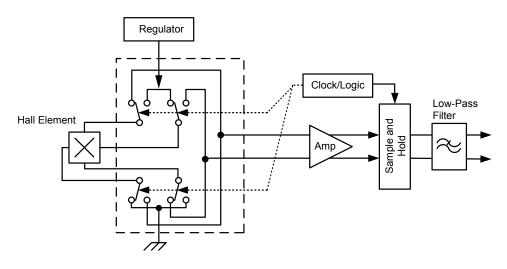

## **CHOPPER STABILIZATION**

A limiting factor for switch point accuracy when using Halleffect technology is the small signal voltage developed across the Hall plate. This voltage is proportionally small relative to the offset that can be produced at the output of the Hall sensor. This makes it difficult to process the signal and maintain an accurate, reliable output over the specified temperature and voltage range. Chopper stabilization is a proven approach used to minimize Hall offset.

The technique, dynamic quadrature offset cancellation, removes key sources of the output drift induced by temperature and package stress. This offset reduction technique is based on a signal modulation-demodulation process. Figure 7: Model of Chopper Stabilization Circuit (Dynamic Offset Cancellation) illustrates how it is implemented.

The undesired offset signal is separated from the magnetically induced signal in the frequency domain through modulation. The subsequent demodulation acts as a modulation process for the offset causing the magnetically induced signal to recover its original spectrum at baseband while the DC offset becomes a high-frequency signal. Then, using a low-pass filter, the signal passes while the modulated DC offset is suppressed. Allegro's innovative chopper-stabilization technique uses a high-frequency clock.

The high-frequency operation allows a greater sampling rate that produces higher accuracy, reduced jitter, and faster signal processing. Additionally, filtering is more effective and results in a lower noise analog signal at the sensor output. Devices such as the APS12000 and APS12060 that use this approach have an extremely stable quiescent Hall output voltage, are immune to thermal stress, and have precise recoverability after temperature cycling. This technique is made possible through the use of a BiCMOS process which allows the use of low offset and low noise amplifiers in combination with high-density logic and sample-and-hold circuits.

Figure 7: Model of Chopper Stabilization Circuit (Dynamic Offset Cancellation)

#### POWER DERATING

The device must be operated below the maximum junction temperature,  $T_{J(max)}$ . Reliable operation may require derating supplied power and/or improving the heat dissipation properties of the application.

Thermal Resistance,  $R_{\theta JA}$  (junction to ambient), is a figure of merit summarizing the ability of the application and the device to dissipate heat from the junction (die), through all paths to ambient air.  $R_{\theta JA}$  is dominated by the Effective Thermal Conductivity, K, of the printed circuit board which includes adjacent devices and board layout. Thermal resistance from the die junction to case,  $R_{\theta JC}$ , is a relatively small component of  $R_{\theta JA}$ . Ambient air temperature,  $T_A$ , and air motion are significant external factors in determining a reliable thermal operating point.

The following three equations can be used to determine operation points for given power and thermal conditions:

$$P_D = V_{IN} \times I_{IN} (1)$$

$$\Delta T = P_D \times R_{\theta JA} (2)$$

$$T_J = T_A + \Delta T (3)$$

#### **Determining Junction Temperature**

For example, given common conditions:  $T_A = 25^{\circ}C$ ,  $V_{CC} = 12 \text{ V}$ ,  $I_{CC} = 2.5 \text{ mA}$ ,  $V_{OUT(SAT)} = 100 \text{ mV}$ ,  $I_{OUT} = 5 \text{ mA}$ , and  $R_{\theta JA} = 165^{\circ}C/W$ , then:

$$\begin{split} P_D &= (V_{CC} \times I_{CC}) + (V_{OUT} \times I_{OUT}) = \\ (12 \ V \times 2.5 \ mA) + (100 \ mV \times 5 \ mA) = \\ 30 \ mW + 0.5 \ mW = 30.5 \ mW \\ \Delta T &= P_D \times R_{\theta JA} = 30.5 \ mW \times 165^{\circ} C/W = 5^{\circ} C \\ T_J &= T_A + \Delta T = 25^{\circ} C + 5^{\circ} C = 30^{\circ} C \end{split}$$

#### Determining Maximum V<sub>CC</sub>

For a given ambient temperature ( $T_A$ ), the maximum allowable power dissipation as a function of  $V_{CC}$  can be calculated.  $P_{D(max)}$ , represents the maximum allowable power level without exceeding  $T_{J(max)}$ , at a selected  $R_{\theta JA}$  and  $T_A$ .

Example: V<sub>CC</sub> estimation using the conditions  $R_{0JA} = 228^{\circ}$ C/W,  $T_{A(max)} = 150^{\circ}$ C,  $T_{J(max)} = 175^{\circ}$ C,  $V_{CC(max)} = 24$  V,  $I_{CC(max)} = 5$  mA,  $V_{OUT} = 500$  mV, and  $I_{OUT} = 20$  mA (output on), calculate the maximum allowable power level,  $P_D(max)$ , first using equation 3:

$$\Delta T_{(max)} = T_{J(max)} - T_A = 175^{\circ}C - 150^{\circ}C = 25^{\circ}C$$

This provides the allowable increase to  $T_J$  resulting from internal power dissipation. Then, using equation 2 first for the output as shown below:

$$P_{D(VOUT)} = V_{OUT} \times I_{OUT} = 500 \text{ mV} \times 20 \text{ mA} = 10 \text{ mW}$$

Then, for the  $V_{CC}$  supply:

$$P_{D(VCC)} = V_{CC} \times I_{CC} = 24 \ V \times 5 \ mA = 120 \ mW$$

Combine the power dissipated by the device pins:

$$P_{D(total)} = (P_{D(VOUT)} + P_{D(VCC)})$$

$$P_{D(total)} = (10 \text{ mW} + 120 \text{ mW}) = 130 \text{ mW}$$

Next, solve for the maximum allowable  $\rm V_{\rm CC}$  for the given conditions using equation 1:

$$V_{CC(est)} = P_{D(total)} \div (I_{CC} + I_{OUT})$$

130 mW ÷ (5 mA + 20 mA)

$$V_{CC(est)} = 130 \text{ mW} \div 25 \text{ mA} = 5.2 \text{ V}$$

The result indicates that, at  $T_A$ , the application and device can dissipate adequate amounts of heat at voltages  $\leq V_{CC(est)}$ .

If the application requires  $V_{CC} > V_{CC(est)}$  then  $R_{\theta JA}$  must by improved. This can be accomplished by adjusting the layout, PCB materials, or by controlling the ambient temperature.

#### Determining Maximum T<sub>A</sub>

In cases where the  $V_{CC(max)}$  level is known, and the system designer would like to determine the maximum allowable ambient temperature,  $T_{A(max)}$ , the calculations can be reversed.

For example, in a worst-case scenario with conditions  $V_{CC(max)} = 24 \text{ V}$ ,  $I_{CC(max)} = 5 \text{ mA}$ ,  $V_{OUT} = 500 \text{ mV}$ ,  $I_{OUT(max)} = 15 \text{ mA}$ , and  $R_{0JA} = 228^{\circ}\text{C/W}$ , for the LH package using equation 1, the largest possible amount of dissipated power is:

$$P_D = V_{IN} \times I_{IN}$$

$$P_D = P_{D(VOUT)} + P_{D(VCC)} = 500 \text{ mV} \times 15 \text{ mA} + 24 \text{ V} \times 5 \text{ mA}$$

$$P_D = 7.5 \text{ mW} + 120 \text{ mW} = 127.5 \text{ mW}$$

Then, by rearranging equation 3:

$$\begin{split} T_{A(max)} &= T_{J(max)} - \varDelta T \\ T_{A(max)} &= 175^{\circ}C - (127.5 \ mW \times 228^{\circ}C/W) \\ T_{A(max)} &= 175^{\circ}C - 29.1^{\circ}C = 145.9^{\circ}C \end{split}$$

Finally, note that the  $T_{A(max)}$  rating of the device is 150°C and performance is not guaranteed above this temperature for any power level.

#### Package LH, 3-Pin SMD (SOT23W) APS12000

#### For Reference Only – Not for Tooling Use (Reference Allegro DWG-0000628, Rev. 1) NOT TO SCALE

(Reference Allegro DW-2000b28, Rev. 1) NOT TO SCALE Dimensions in millimeters Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

#### Package LH, 3-Pin SMD (SOT23W) APS12060

#### For Reference Only – Not for Tooling Use (Reference Allegro DWG-0000628, Rev. 1) NOT TO SCALE

(Reference Allegro DWG-0000628, Rev. 1) NOT TO SCALE Dimensions in millimeters Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

# APS12000 and APS12060

# **Vertical and Planar Hall-Effect Latches**

#### Package UA, 3-Pin SIP APS12000

# APS12000 and APS12060

# **Vertical and Planar Hall-Effect Latches**

### Package UA, 3-Pin SIP APS12060

#### **Revision History**

| Number | Date               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -      | September 13, 2018 | Initial preliminary release                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1      | February 5, 2019   | Updated maximum junction temperature (page 1 and 3), Selection Guide table (page 2), Undervoltage<br>Lockout (page 4), Operate Point (page 5, -0x option minimum value), Power Derating Curve and Power<br>Dissipation versus Ambient Temperature plots (page 6), Undervoltage Lockout description (page 11), Figure 4<br>(page 11), Applications section (page 13), and package branding (pages 16 and 17).<br>Added Magnetic Characteristics plots (page 9-10) and APS12000 part variant (all pages). |

| 2      | April 4, 2019      | Updated Selection Guide (page 2), Character Performance Data plot labels (pages 8-10) , and Power Derating section (page 15).                                                                                                                                                                                                                                                                                                                                                                           |

| 3      | March 10, 2020     | Updated Selection Guide (page 2), Added -3x option magnetic plots (page 11).                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4      | May 12, 2020       | Added "(pending confirmation)" to ASIL references.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5      | June 7, 2022       | Updated package drawings (pages 17-20).                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6      | May 30, 2024       | Fixed broken link (page 14).                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7      | December 3, 2024   | Removed "(pending confirmation)" to ASIL references (pages 1 and 13).                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Copyright 2024, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

<u>Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of</u> <u>Allegro's product can reasonably be expected to cause bodily harm.</u>

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website: www.allegromicro.com