## **ACS732 and ACS733 Evaluation Board**

## ACS732 AND ACS733 DEMO BOARD AND COMPONENTS

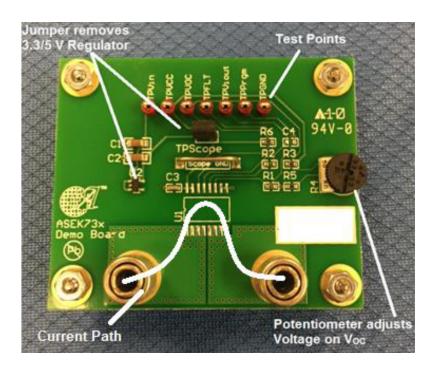

Allegro ACS732/33 demo board is pictured in Figure 1 below. Refer to Table 1 for symbol names and descriptions of onboard components. Note: Board is pictured without Allegro device.

Figure 1: Allegro ACS733 Current Sensor Demo Board

**Table 1: Summary of Demo Board Components**

| Symbol | Description                                                                                           |

|--------|-------------------------------------------------------------------------------------------------------|

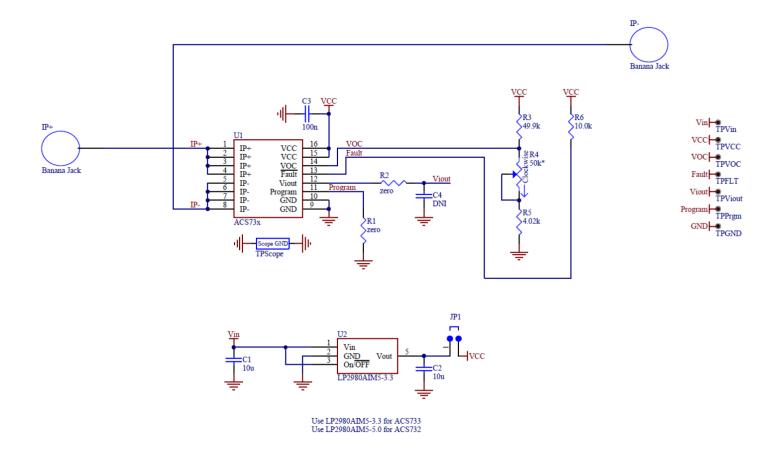

| U1     | Location of Allegro ACS733 (V <sub>CC</sub> = 3.3 V) or ACS732 (V <sub>CC</sub> = 5 V)                |

| U2     | 3.3 or 5 V Regulator                                                                                  |

| Jumper | Removes regulator and capacitors C1, C2 from V <sub>CC</sub> ; C3 (0.1 µF) still present at device    |

| C1, C2 | Regulator output capacitors; removed from the circuit via the jumper                                  |

| C3     | 0.1 μF device bypass capacitor; is always connected                                                   |

| R4     | Potentiometer to set voltage on V <sub>OC</sub> pin; V <sub>OC</sub> voltage sets fault current level |

Figure 2: Schematic for ACS732 and ACS733 Demo Board

## PINOUT DIAGRAM AND TERMINAL LIST

**Table 2: Terminal List Table**

| IP+ 1 | 16 VCC     |

|-------|------------|

| IP+ 2 | 15 VCC     |

| IP+ 3 | 14 VOC     |

| IP+ 4 | 13 FAULT   |

| IP- 5 | 12 VIOUT   |

| IP- 6 | 11 PROGRAM |

| IP- 7 | 10 GND     |

| IP-8  | 9 GND      |

Package LA, 16-Pin SOICW Pinout Diagram

| Number  | Name    | Description                                                                                |

|---------|---------|--------------------------------------------------------------------------------------------|

| 1,2,3,4 | IP+     | Positive terminals for current being sensed; fused internally.                             |

| 5,6,7,8 | IP-     | Negative terminals for current being sensed; fused internally.                             |

| 9,10    | GND     | Device ground terminal.                                                                    |

| 11      | PROGRAM | Programming input pin for factory calibration. Connect to ground for best ESD performance. |

| 12      | VIOUT   | Analog output signal.                                                                      |

| 13      | FAULT   | Overcurrent Fault output. Open drain.                                                      |

| 14      | VOC     | Set the overcurrent fault threshold via external resistor divider on this pin.             |

| 15,16   | VCC     | Device power supply terminal.                                                              |

## **Revision History**

| Number | Date             | Description     |

|--------|------------------|-----------------|

| _      | December 6, 2019 | Initial Release |

Copyright 2019, Allegro MicroSystems.

The information contained in this document does not constitute any representation, warranty, assurance, guaranty, or inducement by Allegro to the customer with respect to the subject matter of this document. The information being provided does not guarantee that a process based on this information will be reliable, or that Allegro has explored all of the possible failure modes. It is the customer's responsibility to do sufficient qualification testing of the final product to ensure that it is reliable and meets all design requirements.

Copies of this document are considered uncontrolled documents.

For the latest version of this document, visit our website:

www.allegromicro.com