#### FEATURES AND BENEFITS

- A<sup>2</sup>-SIL<sup>TM</sup> pending—device features for safety-critical

- Automotive AEC-Q100 qualified

- Wide input voltage range, 3.8 to 36 V<sub>IN</sub> operating range, 40 V<sub>IN</sub> maximum

- 2.2 MHz buck or buck/boost pre-regulator (VREG: 5.35 V) with low EMI frequency dithering

- Frequency dithering and controlled slew rate help reduce EMI/EMC

- Four internal linear regulators with foldback short-circuit protection

- □ VUC: selectable output (3.3 V / 5.0 V) regulator for microcontroller

- □ V5A: 5 V general purpose LDO regulator

- □ V5P1 and V5P2: two LDO regulators with short-tobattery protection for remote sensors

- OV and UV protection for all output rails provides ability to monitor health of outputs

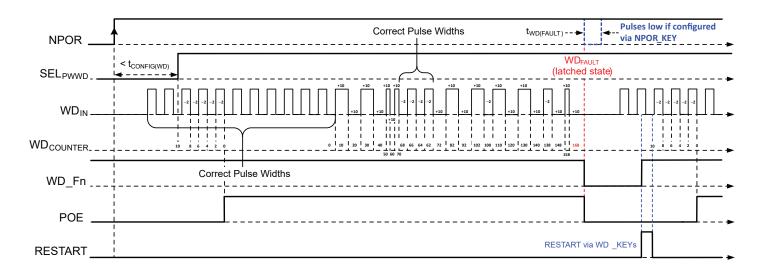

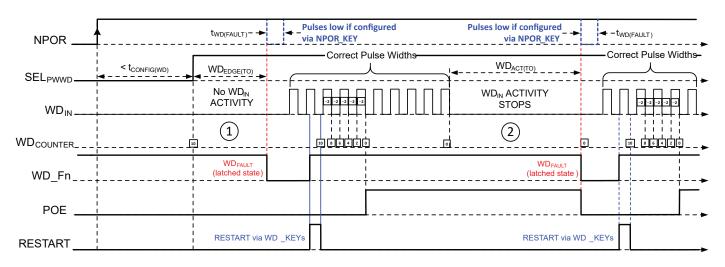

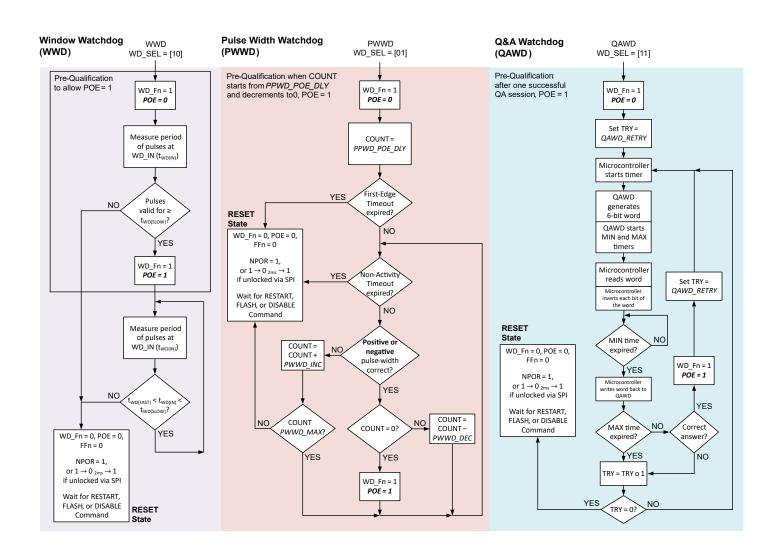

- Pulse Width Watchdog (PWWD), Window Watchdog (WWD), and Q&A Watchdog (QAWD)

- Floating gate drivers (with charge pumps) for external switched load control

- Analog multiplexor (AMUX) reports operational values of multiple important parameters

- Safety signal (POE) can disable a separate function (e.g., motor driver) due to a Watchdog Failure

Continued on next page...

#### **APPLICATIONS**

Provides system power (for microcontroller/DSP, CAN, sensors, etc.) and high-side gate driver control (for motor phases and other switched loads such as solenoid valves and SS relays) in:

- Industrial applications

- Electronic power steering (EPS)

- Advanced braking systems (ABS)

- Transmission control units (TCU)

- Emissions control modules

- Other automotive applications

#### **DESCRIPTION**

The A81407 is ideal for both automotive and industrial applications, where high temperature operation, a high level of integration, and robust solutions are required.

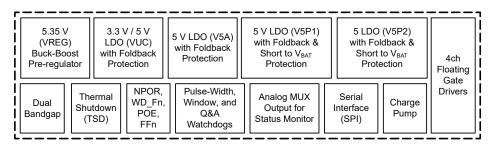

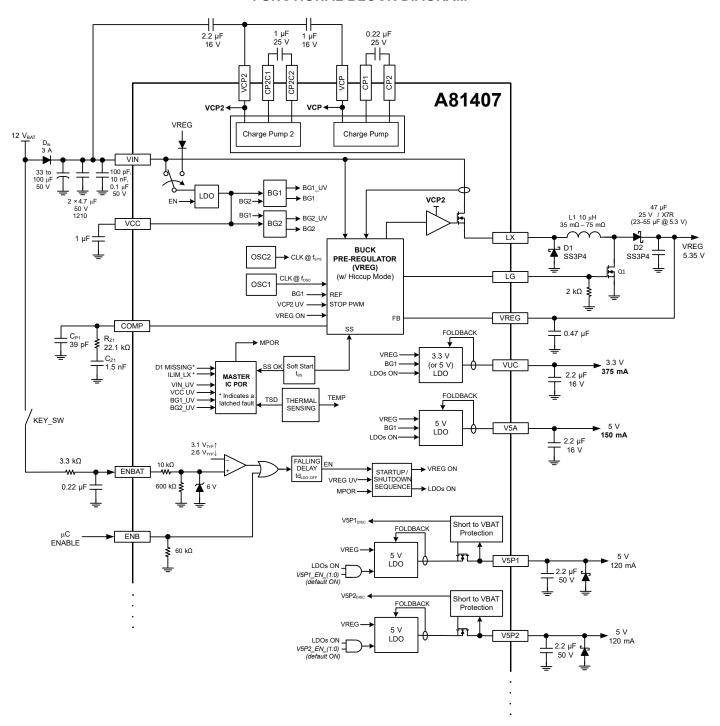

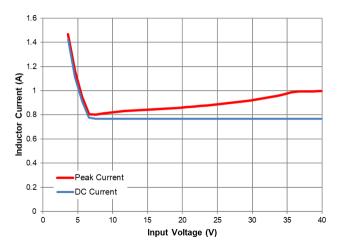

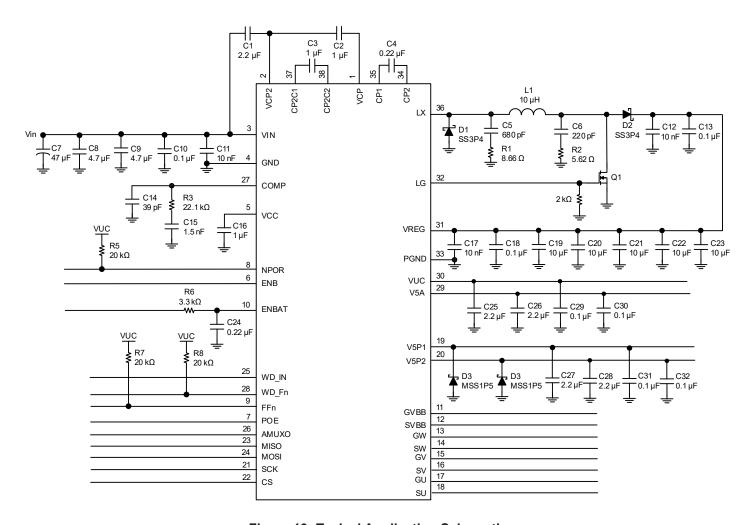

The IC integrates a buck or buck/boost pre-regulator, four LDOs, and four floating gate drivers. The pre-regulator uses a buck or buck/boost topology to efficiently convert input voltages into a tightly regulated intermediate voltage. Frequency dithering and slew control help reduce EMI. The output of the pre-regulator supplies a 3.3 V / 375 mA linear regulator, a 5 V / 150 mA linear regulator, and two 5 V / 120 mA linear regulators. All of the outputs are protected against short circuits, and two are further protected from short-to-supply voltage in case they are used remotely.

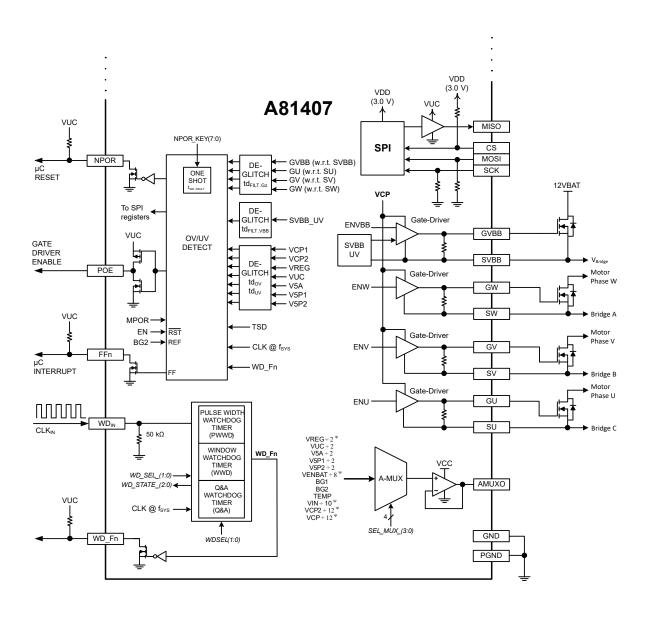

The independent floating gate drivers can be used for input supply disconnect or reverse-supply protection. They can also be used for switched loads such as motor phases, solid state relays, and solenoid valves. They have the capability of controlling N-channel MOSFETs through SPI. An integrated charge pump allows the driver outputs to maintain the power MOSFETs in the on-state over the full supply range with high phase-voltage slew rates.

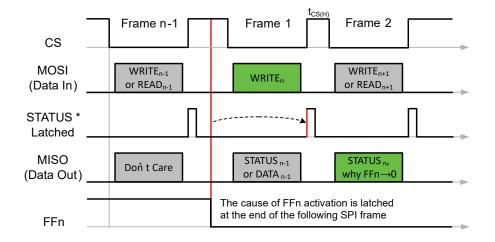

Diagnostic outputs from the A81407 include a Watchdog Fault (WD Fn), power-on reset (NPOR), and a fault flag (FFn) to alert the microprocessor that a fault has occurred. The microprocessor can read fault registers through SPI and operational status via an analog multiplexor.

Continued on next page...

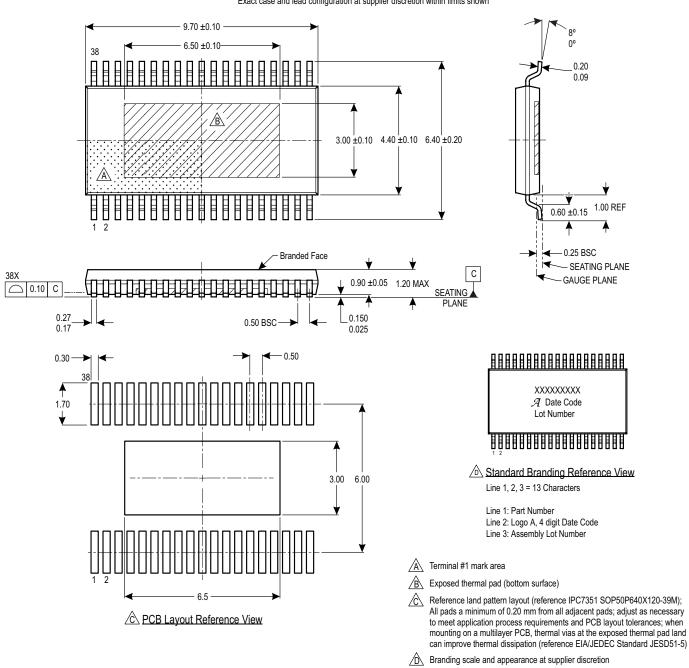

#### **PACKAGE**

38-Pin eTSSOP (suffix LV)

Not to scale

A81407 Simplified Block Diagram

### Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

#### FEATURES AND BENEFITS (continued)

- Pin-to-pin and pin-to-ground tolerant at every pin

- · Control and diagnostic reporting through secure SPI

- □ 16-bit Data Transfers □ 5-bit Message ID

- □ 5-bit CRC □ Read-Back Register

- □ 3-bit Frame Counter □ Chip ID

- Logic enable input (ENB) for microprocessor control

- High-voltage ignition enable input (ENBAT)

- Thermal shutdown protection

- -40°C to 150°C junction temperature range

#### **DESCRIPTION** (continued)

Dual bandgaps, one for regulation and one for fault checking, improve safety coverage and fault detection of the A81407.

The A81407 contains three types of watchdog timers: Pulse Width Watchdog (PWWD), Window Watchdog (WWD), and Q & A Watchdog (QAWD). The watchdog timers can be put into various operating states via secure SPI commands.

The A81407 is supplied in a 38-lead eTSSOP package (suffix "LV") with exposed power pad.

#### **SELECTION GUIDE**

| Part Number    | V <sub>uc</sub> (V) | Package                          | Packing [1]                 | Lead Frame     |  |

|----------------|---------------------|----------------------------------|-----------------------------|----------------|--|

| A81407KLVATR   | 3.3                 | 38-pin eTSSOP with thermal pad   | 4000 pieses per 7 inch real | 100% matte tin |  |

| A81407KLVATR-1 | 5                   | 36-pin e i 330P with thermal pad | 4000 pieces per 7-inch reel | 100% maile im  |  |

#### ABSOLUTE MAXIMUM RATINGS [2]

| Characteristic            | Symbol                                      | Notes                           | Rating                                          | Unit |

|---------------------------|---------------------------------------------|---------------------------------|-------------------------------------------------|------|

| VIN                       | V <sub>VIN</sub>                            |                                 | -0.3 to 40                                      | V    |

| ENBAT                     | V <sub>ENBAT</sub>                          |                                 | -0.3 to 40                                      | V    |

| ENDAI                     | I <sub>ENBAT</sub>                          |                                 | ±75                                             | mA   |

|                           |                                             |                                 | -0.3 to V <sub>VIN</sub> + 0.3                  | V    |

| LX                        | $V_{LX}$                                    | t < 250 ns                      | -1.5                                            | V    |

|                           |                                             | t < 50 ns                       | V <sub>VIN</sub> + 3                            | V    |

| GU, GV, GW, GVBB          | $V_{GU}, V_{GV}, V_{GW}, V_{GVBB}$          |                                 | $V_{Sz} - 0.3$ to $V_{Sz} + 12$                 | V    |

| SU, SV, SW, SVBB          | $V_{SU}$ , $V_{SV}$ , $V_{SW}$ , $V_{SVBB}$ |                                 | −6 to V <sub>VIN</sub> + 5                      | V    |

| VCP (Gate Drivers)        | V <sub>VCP</sub>                            |                                 | $V_{VIN} - 0.3$ to $V_{VIN} + 12$               | V    |

| CP1 (Gate Drivers)        | V <sub>CP1</sub>                            |                                 | $V_{VIN} - 0.3$ to $V_{VIN} + 8$                | V    |

| CP2 (Gate Drivers)        | V <sub>CP2</sub>                            |                                 | V <sub>VIN</sub> – 0.3 to V <sub>VIN</sub> + 12 | V    |

| VCP2 (Pre-Regulator)      | V <sub>VCP2</sub>                           |                                 | $V_{VIN} - 0.3$ to $V_{VIN} + 8$                | V    |

| CP2C1 (Pre-Regulator)     | V <sub>CP2C1</sub>                          |                                 | -0.3 to V <sub>VIN</sub> + 0.3                  | V    |

| CP2C2 (Pre-Regulator)     | V <sub>CP2C2</sub>                          |                                 | $V_{VIN} - 0.3$ to $V_{VIN} + 8$                |      |

| V5P1, V5P2                | V <sub>V5P1</sub> , V <sub>V5P2</sub>       | Independent of V <sub>VIN</sub> | -1.0 to 40                                      | V    |

| All other pins            |                                             |                                 | -0.3 to 7                                       | V    |

| Junction Temperature      | TJ                                          |                                 | -40 to 150                                      | °C   |

| Storage Temperature Range | T <sub>stg</sub>                            |                                 | -40 to 150                                      | °C   |

<sup>[2]</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic                         | Symbol          | Test Conditions [3]    | Value | Unit |

|----------------------------------------|-----------------|------------------------|-------|------|

| Junction to Ambient Thermal Resistance | $R_{\theta JA}$ | eTSSOP-38 (LV) package | 30    | °C/W |

$<sup>\</sup>space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}{\space{1}{3}}\space{1}\space{1}{\space{1}{3}}\space{1}\space{1}{\space{1}{3}}\space{1}\space{1}\space{1}{\space{1}{3}}\space{1}\space{1}{\space{1}{3}}\space{1}\space{1}\space{1}\space{1}\space{1}\space{1}\space{1}\spa$

<sup>[1]</sup> Contact Allegro for additional packing options.

# Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

### **Table of Contents**

| Features and Benefits                  | 1  |

|----------------------------------------|----|

| Description                            | 1  |

| Applications                           | 1  |

| Package                                | 1  |

| Simplified Block Diagram               | 1  |

| Selection Guide                        |    |

| Absolute Maximum Ratings               | 2  |

| Thermal Characteristics                | 2  |

| Functional Block Diagram               | 4  |

| Pinout Diagram and Terminal List Table | 6  |

| Electrical Characteristics             | 7  |

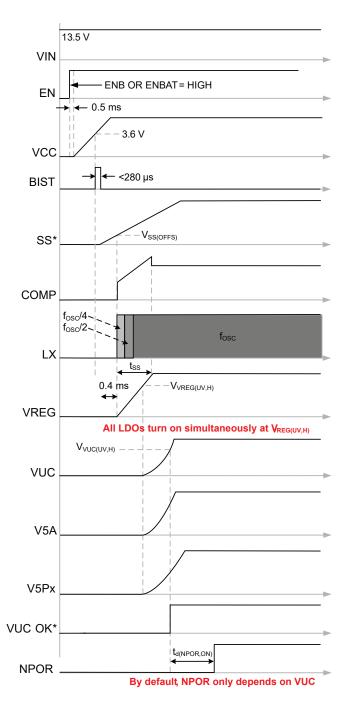

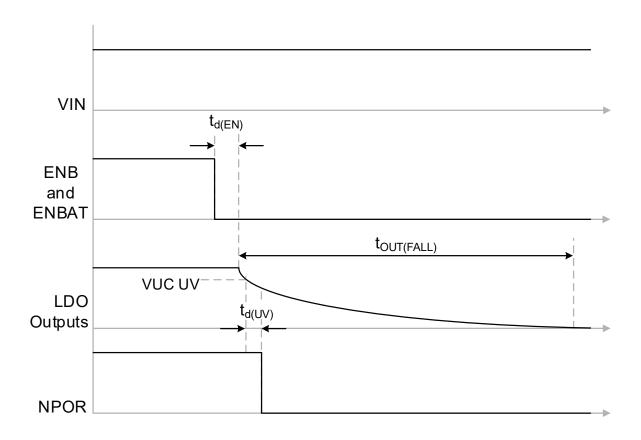

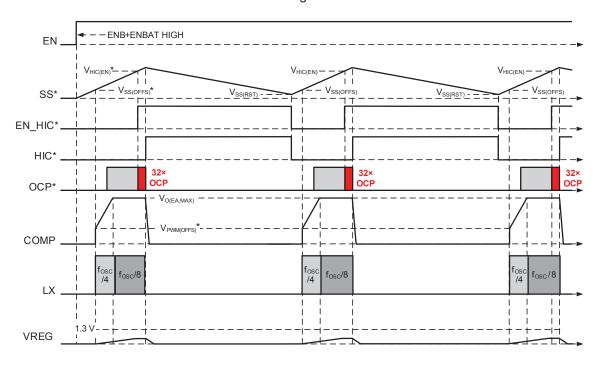

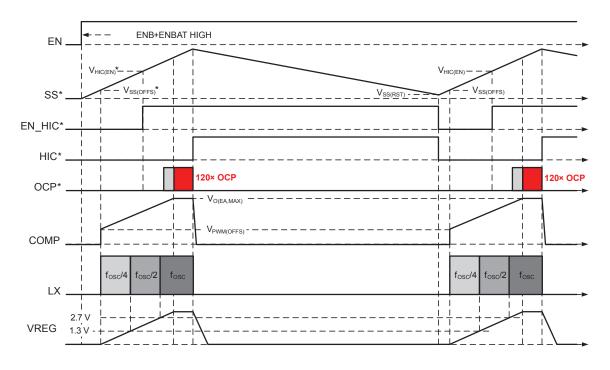

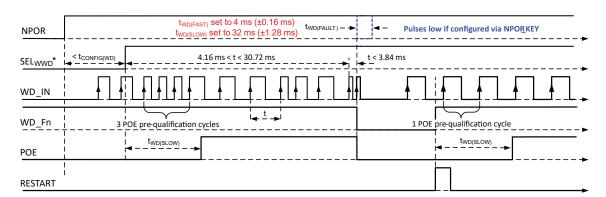

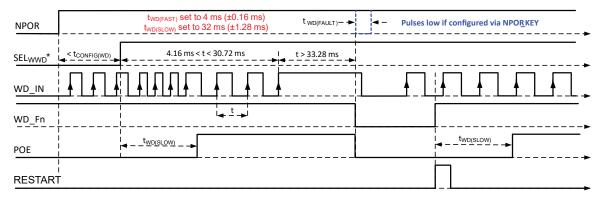

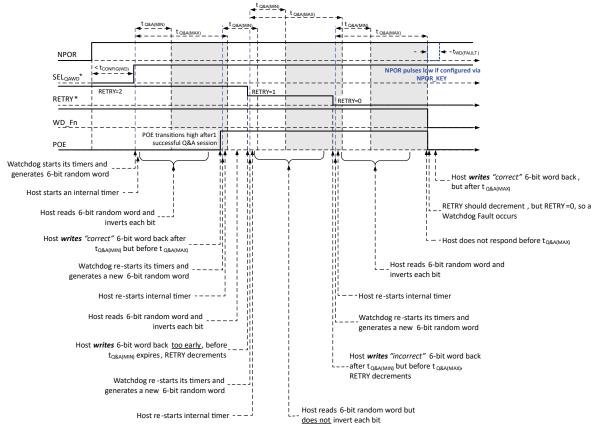

| Timing Diagrams                        | 16 |

| Summary of Fault Mode Operation        | 19 |

| Functional Description                 | 20 |

| Overview                               |    |

| Pre-Regulator (VREG)                   | 20 |

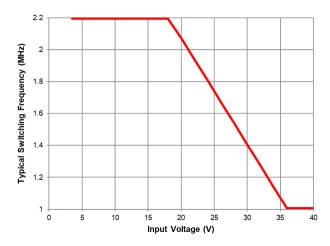

| PWM Switching Frequency                | 20 |

| Bias Supply (VCC)                      | 20 |

| Charge Pump (VCP, VCP2)                          | 20 |

|--------------------------------------------------|----|

| Bandgap (BG1, BG2)                               | 20 |

| Enable Inputs (ENB, ENBAT)                       | 20 |

| Linear Regulators                                | 21 |

| Fault Detection and Reporting (NPOR, WD_Fn, FFn) | 21 |

| Safe State Control Signal (POE)                  | 21 |

| Startup Self-Tests                               | 21 |

| Undervoltage Detect Self-Test                    | 21 |

| Overvoltage Detect Self-Test                     | 21 |

| Overtemperature Shutdown Self-Test               | 21 |

| Power-On Enable (POE) Self-Test                  | 22 |

| Analog Multiplexer Output                        | 22 |

| Floating MOSFET Gate Drivers                     |    |

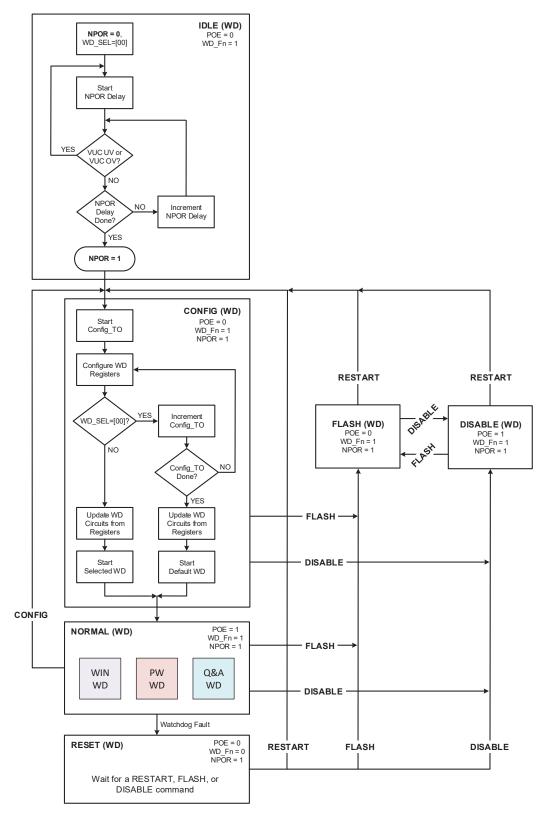

| Watchdog Timers                                  | 22 |

| Serial Communication Interface                   | 30 |

| Register Mapping                                 | 34 |

| Design and Component Selection                   | 51 |

| PCB Layout Recommendations                       |    |

| Package Outline Drawing                          | 57 |

#### **FUNCTIONAL BLOCK DIAGRAM**

### **FUNCTIONAL BLOCK DIAGRAM (continued)**

# Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

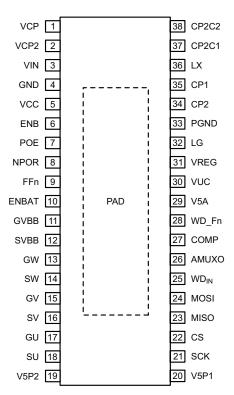

Package LV, 38-Pin eTSSOP Pinout Diagram

#### **Terminal List Table**

| Number | Name  | Function                                                                                                                                 |

|--------|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | VCP   | Charge pump reservoir capacitor connection, for phase disconnects                                                                        |

| 2      | VCP2  | Charge pump reservoir capacitor connection, for buck/boost regulator                                                                     |

| 3      | VIN   | Input voltage pin                                                                                                                        |

| 4      | GND   | Ground                                                                                                                                   |

| 5      | VCC   | Internal voltage regulator bypass capacitor pin                                                                                          |

| 6      | ENB   | Logic enable input from a microcontroller or DSP                                                                                         |

| 7      | POE   | Gate drive enable, latches low to put the system into a safe state                                                                       |

| 8      | NPOR  | Active-low, open-drain VUC fault detection output. Using SPI programming, Watchdog (WD) fault and/or V5A can be added to the NPOR logic. |

| 9      | FFn   | Fault Flag to the microcontroller, open-drain, active low                                                                                |

| 10     | ENBAT | Ignition enable input from the key/switch via a series resistor                                                                          |

| 11     | GVBB  | Battery line MOSFET gate drive                                                                                                           |

| 12     | SVBB  | Battery line MOSFET source reference                                                                                                     |

| 13     | GW    | W phase MOSFET gate drive                                                                                                                |

| 14     | SW    | W phase MOSFET source reference                                                                                                          |

| 15     | GV    | V phase MOSFET gate drive                                                                                                                |

| 16     | SV    | V phase MOSFET source reference                                                                                                          |

| 17     | GU    | U phase MOSFET gate drive                                                                                                                |

| 18     | SU    | U phase MOSFET source reference                                                                                                          |

| 19     | V5P2  | 5 V protected regulator output                                                                                                           |

| 20     | V5P1  | 5 V protected regulator output                                                                                                           |

| 21     | SCK   | SPI clock input from the microcontroller                                                                                                 |

| 22     | CS    | SPI Chip Select input from the microcontroller                                                                                           |

| 23     | MISO  | SPI data output to the microcontroller (Master Input, Slave Output)                                                                      |

| 24     | MOSI  | SPI data input from the microcontroller (Master Output, Slave Input)                                                                     |

| 25     | WDIN  | Watchdog refresh input from a microcontroller or DSP                                                                                     |

| 26     | AMUXO | Analog Multiplexer output                                                                                                                |

| 27     | COMP  | Error amplifier compensation network pin for the buck/boost pre-regulator                                                                |

| 28     | WD_Fn | Open-drain, WD fault output. Latches low if a WD fault is detected.                                                                      |

| 29     | V5A   | 5 V regulator output                                                                                                                     |

| 30     | VUC   | 3.3 V regulator output (or 5V for A81407-1)                                                                                              |

| 31     | VREG  | Voltage feedback input of the pre-regulator and input to the LDOs                                                                        |

| 32     | LG    | Boost gate drive output for the buck/boost pre-regulator                                                                                 |

| 33     | PGND  | Power ground                                                                                                                             |

| 34     | CP2   | Charge pump capacitor connection                                                                                                         |

| 35     | CP1   | Charge pump capacitor connection                                                                                                         |

| 36     | LX    | Switching node for the buck/boost pre-regulator                                                                                          |

| 37     | CP2C1 | Charge pump capacitor connection                                                                                                         |

| 38     | CP2C2 | Charge pump capacitor connection                                                                                                         |

| _      | PAD   | Exposed thermal pad                                                                                                                      |

## Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

| Characteristic                             | Symbol                       | Test Conditions                                                                                             | Min.       | Тур. | Max. | Unit |

|--------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------|------------|------|------|------|

| GENERAL SPECIFICATIONS                     |                              |                                                                                                             |            |      |      |      |

| On a realize or Learney Market area [7]    |                              | After V <sub>VIN</sub> > V <sub>VIN(START)</sub> and VREG in regulating,<br>Buck-Boost Mode                 | 3.8        | 13.5 | 36   | V    |

| Operating Input Voltage [2]                | V <sub>VIN</sub>             | After V <sub>VIN</sub> > V <sub>VIN(START)</sub> and VREG in regulating, Buck Mode                          | 5.5        | 13.5 | 36   | V    |

| VIN UVLO Start Voltage                     | V <sub>VIN(START)</sub>      | V <sub>VIN</sub> rising                                                                                     | 4.55       | 4.8  | 5.05 | V    |

| VIN UVLO Stop Voltage                      | V <sub>VIN(STOP)</sub>       | V <sub>VIN</sub> falling                                                                                    | 3.25       | 3.5  | 3.75 | V    |

| VIN UVLO Hysteresis                        | V <sub>VIN(HYS)</sub>        | V <sub>VIN(START)</sub> – V <sub>VIN(STOP)</sub>                                                            | _          | 1.3  | _    | V    |

|                                            | IQ                           | V <sub>VIN</sub> = 13.5 V, V <sub>VREG</sub> = 5.6 V (no PWM)                                               | _          | 13   | _    | mA   |

| VIN Supply Quiescent Current [1][3]        | I <sub>Q(SLEEP)</sub>        | $V_{VIN}$ = 13.5 V,<br>$V_{ENBAT}$ = Low and $V_{ENB}$ = Low, $T_{J}$ = 25°C                                | -          | -    | 13   | μΑ   |

| PWM SWITCHING FREQUENC                     | Y AND DITHERI                | NG                                                                                                          |            |      |      |      |

| Switching Frequency                        | f <sub>osc</sub>             | Dithering off                                                                                               | 2.0        | 2.2  | 2.4  | MHz  |

| Frequency Dithering                        | Δf <sub>OSC</sub>            | As a percent of f <sub>OSC</sub>                                                                            | _          | ±10  | _    | %    |

| VINI Dish animan Chant Thursday and [2]    |                              | V <sub>VIN</sub> rising                                                                                     | 8.5        | 9.0  | 9.5  | V    |

| VIN Dithering Start Threshold [2]          | V <sub>VIN(DITHER,ON)</sub>  | V <sub>VIN</sub> falling                                                                                    | _          | 17   | _    | V    |

| VINI Distriction Of the Thomas In a Li [2] | V <sub>VIN(DITHER,OFF)</sub> | V <sub>VIN</sub> falling                                                                                    | 7.8        | 8.3  | 8.8  | V    |

| VIN Dithering Stop Threshold [2]           |                              | V <sub>VIN</sub> rising                                                                                     | _          | 18   | _    | V    |

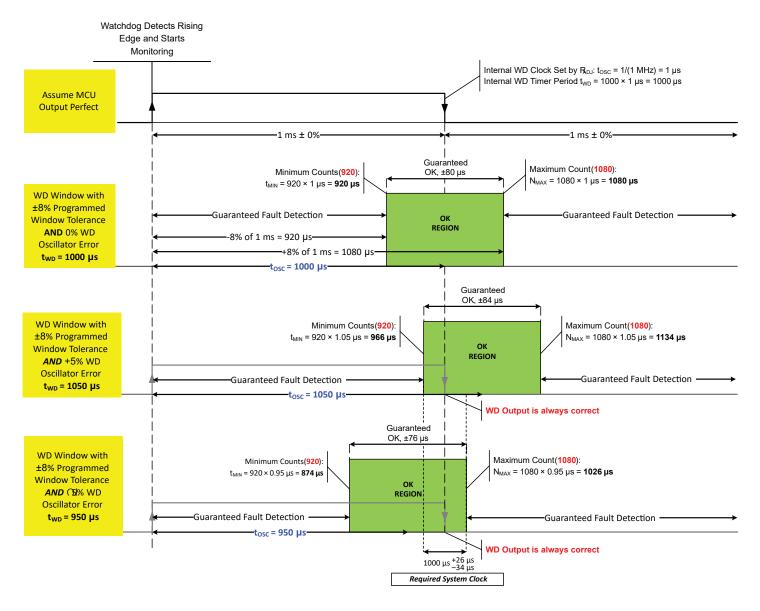

| SYSTEM (WATCHDOG) CLOCK                    |                              |                                                                                                             |            |      |      |      |

| Internal Clock Frequency                   | f <sub>SYS</sub>             |                                                                                                             | _          | 8    | _    | MHz  |

| Internal Clock Tolerance                   | f <sub>SYS(TOL)</sub>        |                                                                                                             | <b>-</b> 5 | _    | +5   | %    |

| CHARGE PUMP (VCP AND VCI                   |                              |                                                                                                             |            |      |      |      |

|                                            |                              | $V_{VCP2} - V_{VIN}, V_{VIN} \ge 9 \text{ V}, I_{VCP2} > -5 \text{ mA},$<br>Buck Mode                       | 4.1        | 6.6  | _    | V    |

| VCP2 Output Voltage<br>(for Pre-Regulator) | V <sub>VCP2</sub>            | $V_{VCP2} - V_{VIN}$ , 5.5 V < $V_{VIN} \le 9$ V, $I_{VCP2} > -5$ mA, Buck Mode                             | 3.6        | 4.4  | _    | V    |

|                                            |                              | $V_{VCP2} - V_{VIN}$ , 3.8 V < $V_{VIN} \le 5.5$ V, $V_{REG} = 5.35$ V, $I_{VCP2} > -5$ mA, Buck-Boost Mode | 3.0        | 3.8  | _    | V    |

|                                            |                              | $V_{VCP} - V_{VIN}, V_{VIN} > 9 \text{ V, } I_{VCP} > -1 \text{ mA,}$<br>Buck Mode                          | 9          | 10   | _    | V    |

| VCP Output Voltage<br>(for Gate Drivers)   | V <sub>VCP</sub>             | $V_{VCP} - V_{VIN}$ , 5.5 V < $V_{VIN} \le 9$ V, $I_{VCP} > -1$ mA, Buck Mode                               | 8          | 10   | _    | V    |

|                                            |                              | $V_{VCP} - V_{VIN}$ , 3.8 V < $V_{VIN} \le 5.5$ V, $V_{VREG} = 5.35$ V, $I_{VCP} > -1$ mA, Buck-Boost Mode  | 6.6        | 9.5  | _    | V    |

| Switching Frequency                        | f <sub>CPx</sub>             |                                                                                                             | _          | 65   | _    | kHz  |

| VCC PIN VOLTAGE                            |                              |                                                                                                             |            |      |      |      |

| Output Voltage                             | V <sub>VCC</sub>             | V <sub>VREG</sub> = 5.35 V                                                                                  | _          | 4.4  | _    | V    |

| THERMAL PROTECTION                         |                              |                                                                                                             |            |      |      |      |

| Thermal Shutdown Threshold [2]             | T <sub>TSD</sub>             | $T_J$ rising                                                                                                | 165        | _    | _    | °C   |

| Thermal Shutdown Hysteresis [2]            | T <sub>HYS</sub>             |                                                                                                             | _          | 15   | _    | °C   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

# Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

| Characteristic                   | Symbol                    | Test Conditions                                                                                                                                         | Min. | Тур. | Max. | Unit |

|----------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| OUTPUT VOLTAGE SPECIFICA         | TIONS                     |                                                                                                                                                         |      |      |      | •    |

| Pre-Regulator Output Voltage [2] | $V_{VREG}$                | V <sub>VIN</sub> = 13.5 V, 0.1 A < I <sub>VREG</sub> < 1.2 A                                                                                            | 5.25 | 5.35 | 5.45 | V    |

| PULSE-WIDTH MODULATION (         | PWM)                      |                                                                                                                                                         |      |      |      |      |

| PWM Ramp Offset                  | V <sub>PWM(OFFS)</sub>    | V <sub>COMP</sub> for 0% duty cycle                                                                                                                     | _    | 480  | _    | mV   |

| LX Rising Slew Rate [2]          | SR <sub>LXRISE</sub>      | V <sub>VIN</sub> = 13.5 V, 10% to 90%, I <sub>VREG</sub> = 1 A                                                                                          | _    | 1.4  | _    | V/ns |

| LX Falling Slew Rate [2]         | SR <sub>LXFALL</sub>      | V <sub>VIN</sub> = 13.5 V, 90% to 10%, I <sub>VREG</sub> = 1 A                                                                                          | _    | 1.5  | _    | V/ns |

| Buck Minimum On-Time             | t <sub>ON(BUCK,MIN)</sub> |                                                                                                                                                         | _    | 85   | 160  | ns   |

| Buck Maximum Duty Cycle          | D <sub>BUCK(MAX)</sub>    | V <sub>VIN</sub> < 7.8 V                                                                                                                                | _    | _    | 100  | %    |

| Boost Duty Cycle                 | D <sub>BST</sub>          | After $V_{VIN} > V_{VIN(START)}$ , VREG regulating, $V_{VIN} = 3.8 \text{ V}$                                                                           | _    | 60   | _    | %    |

|                                  |                           | V <sub>VIN</sub> = 6.5 V                                                                                                                                | _    | 29   | _    | %    |

| COMP to LX Current Gain          | gm <sub>POWER</sub>       |                                                                                                                                                         | _    | 4.57 | _    | A/V  |

| Slope Compensation [2]           | S <sub>E</sub>            |                                                                                                                                                         | 1.1  | 1.62 | 2.15 | A/µs |

| INTERNAL MOSFET                  | ,                         |                                                                                                                                                         |      |      |      |      |

|                                  |                           | $V_{VIN} = 13.5 \text{ V}, T_J = -40^{\circ}\text{C}$ [2], $I_{DS} = 0.1 \text{ A}$                                                                     | _    | 60   | 90   | mΩ   |

| MOSFET On Resistance             | R <sub>DS(on)</sub>       | $V_{VIN}$ = 13.5 V, $T_J$ = 25°C [3], $I_{DS}$ = 0.1 A                                                                                                  | _    | 95   | 115  | mΩ   |

|                                  |                           | V <sub>VIN</sub> = 13.5 V, T <sub>J</sub> = 150°C, I <sub>DS</sub> = 0.1 A                                                                              | _    | 160  | 190  | mΩ   |

| MOSEET Lookogo Current           |                           | $V_{ENBAT} \le 2.2 \text{ V}, V_{ENB} = \text{Low}, V_{LX} = 0 \text{ V}, V_{VIN} = 16 \text{ V}, -40^{\circ}\text{C} < T_{J} < 85^{\circ}\text{C}$ [3] | _    | _    | 10   | μA   |

| MOSFET Leakage Current           | FET(LKG)                  | $V_{ENBAT} \le 2.2 \text{ V}, V_{ENB} \le \text{Low}, V_{LX} = 0 \text{ V}, V_{VIN} = 16 \text{ V}, -40^{\circ}\text{C} < T_{J} < 150^{\circ}\text{C}$  | _    | 50   | 150  | μΑ   |

| ERROR AMPLIFIER                  |                           |                                                                                                                                                         |      |      |      |      |

| Open Loop Voltage Gain           | A <sub>VOL</sub>          |                                                                                                                                                         | _    | 60   | _    | dB   |

| Transconductance                 | aum.                      | V <sub>SS</sub> (internal signal) = 750 mV                                                                                                              | 520  | 720  | 920  | μA/V |

| Transconductance                 | gm <sub>EA</sub>          | V <sub>SS</sub> (internal signal) = 500 mV                                                                                                              | 260  | 360  | 460  | μA/V |

| Output Current                   | I <sub>O(EA)</sub>        |                                                                                                                                                         | _    | ±75  | _    | μA   |

| Maximum Output Valtaga           |                           | V <sub>VIN</sub> < 8.5 V                                                                                                                                | 1.2  | 1.52 | 2.1  | V    |

| Maximum Output Voltage           | V <sub>O(EA,MAX)</sub>    | V <sub>VIN</sub> > 9.5 V                                                                                                                                | 0.9  | 1.22 | 1.7  | V    |

| Minimum Output Voltage           | V <sub>O(EA,MIN)</sub>    |                                                                                                                                                         | _    | _    | 300  | mV   |

| COMP Pull-Down Resistance        | R <sub>COMP</sub>         | HICCUP = 1 or FAULT = 1 or<br>V <sub>ENBAT</sub> = Low and V <sub>ENB</sub> = Low                                                                       | _    | 1    | _    | kΩ   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

# Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

| Characteristic                 | Symbol                    | Test Conditions                                                           | Min. | Тур.                | Max. | Unit          |  |

|--------------------------------|---------------------------|---------------------------------------------------------------------------|------|---------------------|------|---------------|--|

| BOOST MOSFET (LG) GATE DRIVER  |                           |                                                                           |      |                     |      |               |  |

| LG High Output Voltage         | V <sub>LG(ON)</sub>       | V <sub>VIN</sub> = 6 V, V <sub>VREG</sub> = 5.35 V                        | 4.6  | _                   | 5.35 | V             |  |

| LG Low Output Voltage          | V <sub>LG(OFF)</sub>      | V <sub>VIN</sub> = 13.5 V, V <sub>VREG</sub> = 5.35 V                     | _    | 0.2                 | 0.4  | V             |  |

| LG Source Current [1]          | I <sub>LG(ON)</sub>       | V <sub>VIN</sub> = 6 V, V <sub>VREG</sub> = 5.35 V, V <sub>LG</sub> = 1 V | _    | -300                | _    | mA            |  |

| LG Sink Current [1]            | I <sub>LG(OFF)</sub>      | $V_{VIN}$ =13.5 V, $V_{VREG}$ = 5.35 V, $V_{LG}$ = 1 V                    | _    | 150                 | _    | mA            |  |

| SOFT-START                     |                           |                                                                           |      |                     |      |               |  |

| SS Ramp Time [2]               | t <sub>SS</sub>           |                                                                           | _    | 900                 | _    | μs            |  |

|                                |                           | 0 V ≤ V <sub>VREG</sub> < 0.67 V typical                                  | _    | f <sub>OSC</sub> /8 | _    | _             |  |

| SS PWM Frequency Foldback      |                           | 0.67 V ≤ V <sub>VREG</sub> < 1.34 V typical                               | _    | f <sub>OSC</sub> /4 | _    | _             |  |

| 33 FWW Frequency Foldback      | f <sub>SW(SS)</sub>       | 1.34 V ≤ V <sub>VREG</sub> < 2.68 V typical                               | _    | f <sub>OSC</sub> /2 | _    | _             |  |

|                                |                           | V <sub>VREG</sub> ≥ 2.68 V typical                                        | _    | f <sub>OSC</sub>    | _    | _             |  |

| HICCUP MODE                    |                           |                                                                           |      |                     |      |               |  |

| Hiccup Enable Delay Time [2]   | t <sub>HIC(EN)</sub>      |                                                                           | _    | 230                 | _    | μs            |  |

| Hiccup Recovery Time [2]       | t <sub>HIC(REC)</sub>     |                                                                           | _    | 930                 | _    | μs            |  |

| History OCD DWM Counts         |                           | $V_{VREG}$ < 1.3 $V_{TYP}$ , $V_{COMP} = V_{O(EA,MAX)}$                   | -    | 32                  | _    | PWM<br>cycles |  |

| Hiccup OCP PWM Counts          | t <sub>HIC(OCP)</sub>     | $V_{VREG} > 1.3 V_{TYP}, V_{COMP} = V_{O(EA,MAX)}$                        | -    | 120                 | _    | PWM<br>cycles |  |

| CURRENT PROTECTIONS            |                           |                                                                           |      |                     |      |               |  |

| Pulse by Pulse Current Limit   |                           | V <sub>VIN</sub> < 8.5 V                                                  | 3.83 | 4.2                 | 4.77 | Α             |  |

| Pulse-by-Pulse Current Limit   | I <sub>LIM(ton,min)</sub> | V <sub>VIN</sub> > 9.5 V                                                  | 2.49 | 2.8                 | 3.11 | А             |  |

| LX Short-Circuit Current Limit | I <sub>LIM(LX)</sub>      | Latched fault after 2 <sup>nd</sup> detection                             | 5.3  | 7.1                 | _    | Α             |  |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

## Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

| Characteristic                                           | Symbol                 | Test Conditions                                               | Min. | Тур. | Max. | Unit |

|----------------------------------------------------------|------------------------|---------------------------------------------------------------|------|------|------|------|

| MISSING ASYNCHRONOUS DIODE                               | (D1) PROTE             | CTION                                                         |      | ,    |      |      |

| Detection Level                                          | V <sub>D(OPEN)</sub>   |                                                               | -1.9 | -1.4 | -1.0 | V    |

| Time Filtering [2]                                       | t <sub>D(OPEN)</sub>   |                                                               | 50   | _    | 250  | ns   |

| VUC, V5A, V5Px LINEAR REGULAT                            | ORS                    |                                                               |      |      |      |      |

| VUC Accuracy and Load Regulation (5 V <sub>OUT</sub> )   | V <sub>VUC5</sub>      | 10 mA < I <sub>VUC</sub> < 375 mA, V <sub>VREG</sub> = 5.25 V | 4.9  | 5.0  | 5.1  | V    |

| VUC Accuracy and Load Regulation (3.3 V <sub>OUT</sub> ) | V <sub>VUC33</sub>     | 10 mA < I <sub>VUC</sub> < 375 mA, V <sub>VREG</sub> = 5.25 V | 3.23 | 3.30 | 3.37 | V    |

| VUC Output Capacitance Range [2]                         | C <sub>OUT(VUC)</sub>  |                                                               | 1.0  | _    | 15   | μF   |

| V5A Accuracy and Load Regulation                         | V <sub>V5A</sub>       | 5 mA < I <sub>V5A</sub> < 150 mA, V <sub>VREG</sub> = 5.25 V  | 4.9  | 5.0  | 5.1  | V    |

| V5A Output Capacitance Range [2]                         | C <sub>OUT(V5A)</sub>  |                                                               | 1.0  | _    | 15   | μF   |

| V5Px Accuracy and Load Regulation                        | V <sub>V5Px</sub>      | 5 mA < I <sub>V5Px</sub> < 120 mA, V <sub>VREG</sub> = 5.25 V | 4.9  | 5.0  | 5.1  | V    |

| V5Px Output Capacitance Range [2]                        | C <sub>OUT(V5Px)</sub> |                                                               | 1.0  | _    | 15   | μF   |

| VUC OVERCURRENT PROTECTION                               |                        |                                                               |      |      |      |      |

| VUC Current Limit [1]                                    | I <sub>VUC(LIM)</sub>  |                                                               | -412 | -625 | -880 | mA   |

| VUC Foldback Current [1]                                 | I <sub>VUC(FBK)</sub>  | V <sub>VUC</sub> = 0 V                                        | -65  | -187 | -275 | mA   |

| V5A OVERCURRENT PROTECTION                               | I                      |                                                               |      |      |      |      |

| V5A Current Limit [1]                                    | I <sub>V5A(LIM)</sub>  |                                                               | -160 | -235 | -325 | mA   |

| V5A Foldback Current [1]                                 | I <sub>V5A(FBK)</sub>  | V <sub>V5A</sub> = 0 V                                        | -20  | -78  | -163 | mA   |

| V5Px OVERCURRENT PROTECTIO                               | N                      |                                                               |      |      |      |      |

| V5Px Current Limit [1]                                   | I <sub>V5Px(LIM)</sub> |                                                               | -135 | -230 | -350 | mA   |

| V5Px Foldback Current [1]                                | I <sub>V5Px(FBK)</sub> | V <sub>V5Px</sub> = 0 V                                       | -20  | -60  | -125 | mA   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

# Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

| Characteristic                                                      | Symbol                    | Test Conditions                                   | Min. | Тур. | Max. | Unit |  |

|---------------------------------------------------------------------|---------------------------|---------------------------------------------------|------|------|------|------|--|

| VUC, V5A, AND V5Px STARTUP TIMING                                   |                           |                                                   |      |      |      |      |  |

| VUC Startup Time (5 V <sub>OUT</sub> ) [2]                          | t <sub>VUC5(START)</sub>  | C <sub>VUC</sub> = 2.2 μF ±20%, Load = 15 Ω ±10%  | _    | 0.15 | 1.0  | ms   |  |

| VUC Startup Time (3.3 V <sub>OUT</sub> ) [2]                        | t <sub>VUC33(START)</sub> | $C_{VUC}$ = 2.2 µF ±20%, Load = 10 $\Omega$ ±10%  | _    | 0.13 | 0.65 | ms   |  |

| V5A Startup Time [2]                                                | t <sub>V5(START)</sub>    | $C_{V5A}$ = 2.2 µF ±20%, Load = 40 $\Omega$ ±10%  | _    | 0.22 | 1.2  | ms   |  |

| V5Px Startup Time [2]                                               | t <sub>V5Px(START)</sub>  | $C_{V5Px}$ = 2.2 µF ±20%, Load = 50 $\Omega$ ±10% | _    | 0.22 | 1.2  | ms   |  |

| IGNITION ENABLE (ENBAT) INPUT                                       | Г                         |                                                   |      |      |      |      |  |

| ENBAT Upper Threshold                                               | V <sub>ENBAT(H)</sub>     | V <sub>ENBAT</sub> rising                         | 2.7  | 3.1  | 3.5  | V    |  |

| ENBAT Lower Threshold                                               | V <sub>ENBAT(L)</sub>     | V <sub>ENBAT</sub> falling                        | 2.2  | 2.6  | 2.9  | V    |  |

| ENBAT Hysteresis                                                    | V <sub>ENBAT(HYS)</sub>   | V <sub>ENBAT(H)</sub> – V <sub>ENBAT(L)</sub>     | _    | 500  | _    | mV   |  |

| ENBAT Bias Current [1]                                              |                           | V <sub>ENBAT</sub> = 3.5 V                        | _    | 20   | 50   | μA   |  |

| ENDAT bias Currentin                                                | I <sub>ENBAT(BIAS)</sub>  | V <sub>ENBAT</sub> = 40 V                         | _    | _    | 5.5  | mA   |  |

| ENBAT Pulldown Resistance                                           | R <sub>ENBAT</sub>        | V <sub>ENBAT</sub> < 1.2 V                        | _    | 600  | _    | kΩ   |  |

| LOGIC ENABLE (ENB) INPUT                                            |                           |                                                   |      | `    |      |      |  |

| ENB Upper Threshold                                                 | V <sub>ENB(H)</sub>       | V <sub>ENB</sub> rising                           | _    | _    | 2.0  | V    |  |

| ENB Lower Threshold                                                 | V <sub>ENB(L)</sub>       | V <sub>ENB</sub> falling                          | 0.8  | _    | -    | V    |  |

| ENB Bias Current [1]                                                | I <sub>ENB(IN)</sub>      | V <sub>ENB</sub> = 3.3 V                          | _    | _    | 175  | μA   |  |

| ENB Resistance                                                      | R <sub>ENB</sub>          |                                                   | _    | 60   | _    | kΩ   |  |

| ENB/ENBAT DELAY                                                     |                           |                                                   | ,    |      |      |      |  |

| Enable Falling Delay Time                                           | t <sub>dLDO(OFF)</sub>    |                                                   | 10   | 15   | 20   | μs   |  |

| VUC, V5A, AND V5Px UNDERVOLT                                        | AGE DETECT                | ION THRESHOLDS                                    |      | `    |      |      |  |

| VUC (5 V <sub>OUT</sub> ), V5A, and V5Px                            | V <sub>V5(UV,H)</sub>     | V <sub>V5</sub> rising                            | _    | 4.68 | _    | V    |  |

| Undervoltage Thresholds                                             | V <sub>V5(UV,L)</sub>     | V <sub>V5</sub> falling                           | 4.50 | 4.65 | 4.80 | V    |  |

| VUC (5 V <sub>OUT</sub> ), V5A, and V5Px<br>Undervoltage Hysteresis | V <sub>V5(UV,HYS)</sub>   | V <sub>V5(UV,H)</sub> – V <sub>V5(UV,L)</sub>     | _    | 30   | -    | mV   |  |

| VUC (3.3 V <sub>OUT</sub> )                                         | V <sub>3V3(UV,H)</sub>    | V <sub>3V3</sub> rising                           | _    | 3.12 | _    | V    |  |

| Undervoltage Thresholds                                             | V <sub>3V3(UV,L)</sub>    | V <sub>3V3</sub> falling                          | 2.8  | 3.1  | 3.19 | V    |  |

| VUC (3.3 V <sub>OUT</sub> )<br>Undervoltage Hysteresis              | V <sub>3V3(UV,HYS)</sub>  | V <sub>3V3(UV,H)</sub> – V <sub>3V3(UV,L)</sub>   | _    | 20   | -    | mV   |  |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

## Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

| Characteristic                                                     | Symbol                    | Test Conditions                                                                                      | Min. | Тур. | Max. | Unit |  |  |

|--------------------------------------------------------------------|---------------------------|------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|

| VUC, V5A, V5P1, AND V5P2 OVERVOLTAGE PROTECTION THRESHOLDS         |                           |                                                                                                      |      |      |      |      |  |  |

| VUC (5 V <sub>OUT</sub> ), V5A, and V5Px<br>Overvoltage Thresholds | V <sub>V5(OV,H)</sub>     | V <sub>V5A</sub> rising                                                                              | 5.15 | 5.33 | 5.5  | V    |  |  |

|                                                                    | V <sub>V5(OV,L)</sub>     | V <sub>V5A</sub> falling                                                                             | _    | 5.30 | _    | V    |  |  |

| VUC (5 V <sub>OUT</sub> ), V5A, and V5Px<br>Overvoltage Hysteresis | V <sub>V5(OV,HYS)</sub>   | $V_{V5A(OV,H)} - V_{V5A(OV,L)}$                                                                      | _    | 30   | _    | mV   |  |  |

| V5Px Output Disconnect Threshold                                   | V <sub>V5Px(DISC)</sub>   | V <sub>V5Px</sub> rising                                                                             | _    | 7.2  | _    | V    |  |  |

| VUC (3.3 V <sub>OUT</sub> )                                        | V <sub>3V3(OV,H)</sub>    | V <sub>3V3</sub> rising                                                                              | 3.45 | 3.51 | 3.66 | V    |  |  |

| Overvoltage Thresholds                                             | V <sub>3V3(OV,L)</sub>    | V <sub>3V3</sub> falling                                                                             | _    | 3.49 | _    | V    |  |  |

| VUC (3.3 V <sub>OUT</sub> )<br>Overvoltage Hysteresis              | V <sub>3V3(OV,HYS)</sub>  | $V_{3V3(OV,H)} - V_{3V3(OV,L)}$                                                                      | _    | 20   | _    | mV   |  |  |

| VREG, VCPx, AND BG THRESHOL                                        | DS                        |                                                                                                      |      |      |      |      |  |  |

| VREG Non-Latching Overvoltage                                      | V <sub>VREG(OV,H)</sub>   | V <sub>VREG</sub> rising, LX PWM disabled                                                            | 5.70 | 5.95 | 6.20 | V    |  |  |

| Threshold                                                          | V <sub>VREG(OV,L)</sub>   | V <sub>VREG</sub> falling, LX PWM enabled                                                            | _    | 5.85 | _    | V    |  |  |

| VREG Non-Latching Overvoltage Hysteresis                           | V <sub>VREG(OV,HYS)</sub> | $V_{VREG(OV,H)} - V_{VREG(OV,L)}$                                                                    | _    | 100  | _    | mV   |  |  |

| VREG Undervoltage Thresholds                                       | V <sub>VREG(UV,H)</sub>   | V <sub>VREG</sub> rising, triggers rise of VUC linear regulator                                      | 4.50 | 4.75 | 5.00 | V    |  |  |

|                                                                    | V <sub>VREG(UV,L)</sub>   | V <sub>VREG</sub> falling                                                                            | _    | 4.65 | _    | V    |  |  |

| VREG Undervoltage Hysteresis                                       | V <sub>VREG(UV,HYS)</sub> | $V_{VREG(UV,H)} - V_{VREG(UV,L)}$                                                                    | _    | 100  | _    | mV   |  |  |

| VCP2 Overvoltage Thresholds                                        | V <sub>VCP2(OV,H)</sub>   | Detected on CP2C1 pin.<br>Defined as V <sub>VIN</sub> – V <sub>CP2C1</sub> , V <sub>VIN</sub> ≥ 14 V | 11.0 | 12.5 | 14.0 | V    |  |  |

| VCP2 Undervoltage Thresholds                                       | V <sub>VCP2(UV,H)</sub>   | V <sub>VCP2</sub> rising, PWM enabled (w.r.t. V <sub>VIN</sub> )                                     | 2.78 | 3.1  | 3.26 | V    |  |  |

| (Pre-Regulator)                                                    | V <sub>VCP2(UV,L)</sub>   | V <sub>VCP2</sub> falling, PWM disabled (w.r.t. V <sub>VIN</sub> )                                   | _    | 2.8  | _    | V    |  |  |

| VCP2 Undervoltage Hysteresis                                       | V <sub>VCP2(UV,HYS)</sub> | $V_{VCP2(UV,H)} - V_{VCP2(UV,L)}$                                                                    | _    | 400  | _    | mV   |  |  |

| VCP Undervoltage Thresholds                                        | V <sub>VCP(UV,H)</sub>    | V <sub>VCP</sub> rising, PWM enabled (w.r.t. V <sub>VIN</sub> )                                      | 5.71 | 6.3  | 6.63 | V    |  |  |

| VCF Officervoltage Tiffesholds                                     | V <sub>VCP(UV,L)</sub>    | V <sub>VCP</sub> falling, PWM disabled (w.r.t. V <sub>VIN</sub> )                                    | _    | 5.1  | _    | V    |  |  |

| VCP Undervoltage Hysteresis                                        | V <sub>VCP(UV,HYS)</sub>  | $V_{VCP(UV,H)} - V_{VCP(UV,L)}$                                                                      | _    | 1.2  | _    | V    |  |  |

| BG1 and BG2 Undervoltage<br>Thresholds <sup>[2]</sup>              | V <sub>BGx(UV)</sub>      | V <sub>BG1</sub> or V <sub>BG2</sub> falling                                                         | 1.00 | 1.05 | 1.10 | V    |  |  |

| OVERVOLTAGE FILTERING/DEGL                                         | ITCH TIME                 |                                                                                                      |      |      |      |      |  |  |

| Overvoltage Detection Delay [2]                                    | t <sub>d(OV)</sub>        | Overvoltage detection delay time                                                                     | 5    | _    | 25   | μs   |  |  |

| UNDERVOLTAGE FILTERING/DEG                                         | LITCH TIME                |                                                                                                      |      |      |      |      |  |  |

| Undervoltage Filter/Deglitch Times [2]                             | t <sub>d(UV)</sub>        | Undervoltage detection delay time                                                                    | 5    | _    | 25   | μs   |  |  |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking)

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

## Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

| Characteristic                                   | Symbol                  | Test Conditions                                                                                                | Min.                   | Тур. | Max. | Unit |

|--------------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------|------------------------|------|------|------|

| NPOR TURN-ON AND TURN-OFF                        | ELAYS                   |                                                                                                                |                        |      | `    |      |

| NPOR Turn-On Delay                               | t <sub>d(NPOR,ON)</sub> | Time from VUC > V <sub>3V3(UV,H)</sub> (or V <sub>V5(UV,H)</sub> ) to when the NPOR pin becomes high impedance | 3.7                    | 5    | 6.3  | ms   |

| NPOR OUTPUT VOLTAGES                             | '                       |                                                                                                                |                        |      |      |      |

| NPOR Output Low Voltage                          | W                       | I <sub>NPOR</sub> = 4 mA                                                                                       | _                      | 150  | 400  | mV   |

| NPOR Output Low Voltage                          | V <sub>NPOR(L)</sub>    | V <sub>VIN</sub> = 5.5 V, I <sub>NPOR</sub> = 2 mA                                                             | -                      | -    | 200  | mV   |

| NPOR Leakage Current [1]                         | I <sub>NPOR(LKG)</sub>  | V <sub>NPOR</sub> = 3.3 V                                                                                      | _                      | _    | 2    | μΑ   |

| NPOR ONE-SHOT TIME (ONLY if en                   | abled via SPI u         | sing the NPOR_KEY)                                                                                             |                        |      |      |      |

| NPOR One-Shot "Low" Time After<br>Watchdog Fault | t <sub>WD(FAULT)</sub>  |                                                                                                                | 1.6                    | 2    | 2.4  | ms   |

| FAULT FLAG OUTPUT VOLTAGES                       | (FFn)                   |                                                                                                                |                        |      |      |      |

| FFn Output Voltage                               | V <sub>FFn(L)</sub>     | FFn is tripped, I <sub>FFn</sub> = 2 mA                                                                        | _                      | 150  | 400  | mV   |

| FFn Leakage Current                              | I <sub>FFn(LKG)</sub>   | V <sub>FFn</sub> = 3.3 V                                                                                       | _                      | _    | 2    | μΑ   |

| WD <sub>IN</sub> VOLTAGE THRESHOLDS AN           | D RESISTANO             | CE                                                                                                             |                        |      |      |      |

| WD <sub>IN</sub> Upper Threshold                 | V <sub>WDIN(HI)</sub>   | V <sub>WDIN</sub> rising                                                                                       | -                      | -    | 2.0  | V    |

| WD <sub>IN</sub> Lower Threshold                 | V <sub>WDIN(LO)</sub>   | V <sub>WDIN</sub> falling                                                                                      | 0.8                    | _    | _    | V    |

| WD <sub>IN</sub> Pull-Down Resistance [2]        | R <sub>WDIN</sub>       |                                                                                                                | _                      | 50   | _    | kΩ   |

| WD TIMING SPECIFICATIONS                         |                         |                                                                                                                |                        |      |      |      |

| Watchdog Configuration Time                      | t <sub>CONFIG(WD)</sub> | Can be bypassed by setting WD_SEL bits                                                                         | _                      | 1000 | _    | ms   |

| WD_Fn OUTPUT SPECIFICATIONS                      | }                       |                                                                                                                |                        |      |      |      |

| Output Law Valtage                               | \                       | I <sub>WD_Fn</sub> = 4 mA                                                                                      | -                      | 150  | 400  | mV   |

| Output Low Voltage                               | $V_{WD\_Fn(L)}$         | V <sub>VIN</sub> = 5.5 V, I <sub>WD_Fn</sub> = 1 mA                                                            | _                      | -    | 200  | mV   |

| Leakage Current                                  | I <sub>WD_Fn(LKG)</sub> | V <sub>WD_Fn</sub> = 3.3 V                                                                                     | -                      | _    | 2    | μΑ   |

| GATE DRIVE ENABLE (POE)                          |                         |                                                                                                                |                        |      |      |      |

| POE Output Voltage                               | V <sub>POE(L)</sub>     | I <sub>POE</sub> = 4 mA                                                                                        | _                      | 150  | 400  | mV   |

| 1 OL Output voltage                              | V <sub>POE(H)</sub>     | $I_{POE} = -1.5 \text{ mA}$                                                                                    | 0.8 × V <sub>VUC</sub> | _    | _    | V    |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

| Characteristic                                     | Symbol                | Test Conditions                               | Min.                   | Тур. | Max. | Unit |

|----------------------------------------------------|-----------------------|-----------------------------------------------|------------------------|------|------|------|

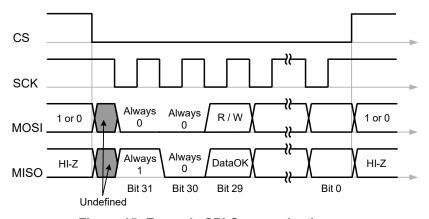

| SERIAL INTERFACE (STRn, SDI, SD                    | O, SCK)               |                                               |                        |      |      |      |

| Input Low Voltage                                  | V <sub>IL</sub>       |                                               | _                      | _    | 0.8  | V    |

| Input High Voltage                                 | V <sub>IH</sub>       | All logic inputs                              | 2.0                    | _    | -    | V    |

| Input Hysteresis                                   | V <sub>Ihys</sub>     | All logic inputs                              | 250                    | 550  | _    | mV   |

| MOSI and SCK Input Pull-Down                       | R <sub>PD</sub>       | V <sub>MOSI</sub> or V <sub>SCK</sub> = 3.3 V | _                      | 50   | _    | kΩ   |

| CS Input Pull-Up to 3.0 V                          | R <sub>PU</sub>       |                                               | _                      | 50   | _    | kΩ   |

| Output Low Voltage                                 | V <sub>OL</sub>       | I <sub>OL</sub> = 1 mA <sup>[1]</sup>         | _                      | _    | 0.4  | V    |

| Output High Voltage                                | V <sub>OH</sub>       | I <sub>OL</sub> = -1 mA <sup>[1]</sup>        | 0.8 × V <sub>VUC</sub> | _    | _    | V    |

| SPI Clock Frequency [2]                            | f <sub>SCK</sub>      | MISO pins, C <sub>L</sub> = 20 pF             | 0.1                    | _    | 10   | MHz  |

| SPI Frame Rate [2]                                 | t <sub>SPI</sub>      |                                               | 2.94                   | _    | 294  | kHz  |

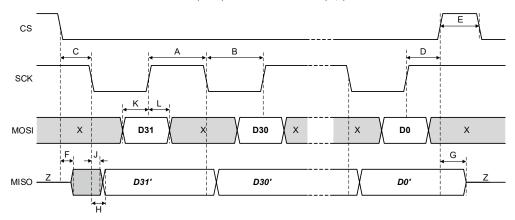

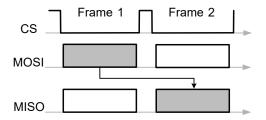

| Clock High Time                                    | t <sub>SCK(H)</sub>   | A in Figure 1                                 | 40                     | _    | _    | ns   |

| Clock Low Time                                     | t <sub>SCK(L)</sub>   | B in Figure 1                                 | 40                     | _    | _    | ns   |

| Chip Select Lead Time                              | t <sub>CS(LD)</sub>   | C in Figure 1                                 | 30                     | _    | _    | ns   |

| Chip Select Lag Time                               | t <sub>CS(LG)</sub>   | D in Figure 1                                 | 30                     | _    | _    | ns   |

| Chip Select High Time                              | t <sub>CS(H)</sub>    | E in Figure 1                                 | 300                    | _    | _    | ns   |

| Data Out (MISO) Enable Time [2]                    | t <sub>MISO(EN)</sub> | F in Figure 1                                 | _                      | _    | 40   | ns   |

| Data Out (MISO) Disable Time [2]                   | t <sub>MISO(D)</sub>  | G in Figure 1                                 | -                      | _    | 30   | ns   |

| Data Out (MISO) Valid Time<br>From SCK Falling [2] | t <sub>MISO(V)</sub>  | H in Figure 1                                 | -                      | -    | 40   | ns   |

| Data Out (MISO) Hold Time<br>From SCK Falling [2]  | t <sub>MISO(H)</sub>  | J in Figure 1                                 | 5                      | -    | -    | ns   |

| Data In (MOSI) Set-Up Time<br>To SCK Rising        | t <sub>MOSI(SU)</sub> | K in Figure 1                                 | 15                     | -    | -    | ns   |

| Data In (MOSI) Hold Time<br>From SCK Rising        | t <sub>MOSI(H)</sub>  | L in Figure 1                                 | 10                     | -    | -    | ns   |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin (sinking).

<sup>[4]</sup> The lowest operating voltage is only valid if the conditions  $V_{VIN} > V_{VIN(START)}$  and  $V_{VCP} - V_{VIN} > V_{VCP(UV,H)}$  and  $V_{VREG}$  in regulating are satisfied before  $V_{VIN}$  is reduced.

Figure 1: Serial Interface Timing for Write and Read Cycles MISO activity assumes the Chip\_ID from the previous frame was correct

<sup>[2]</sup> Ensured by design and characterization, not production tested.

<sup>[3]</sup> Specifications at 25°C or 85°C are guaranteed by design and characterization, not production tested.

## Multi-Output Regulator with Buck or Buck-Boost Pre-Regulator, 4× LDO Outputs, Watchdog, 4× Gate Drivers, and SPI

| Characteristic                                                    | Symbol                                      | Test Conditions                                                                                                                                                   | Min. | Тур. | Max.                 | Unit |

|-------------------------------------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------------------|------|

| <b>GATE OUTPUT DRIVE</b> $(z = U, V, W)$                          |                                             |                                                                                                                                                                   |      |      |                      |      |

| Turn-On Time                                                      | t <sub>r</sub>                              | C <sub>LOAD</sub> = 10 nF, 20% to 80%                                                                                                                             | _    | 5    | _                    | μs   |

| Turn-Off Time                                                     | t <sub>f</sub>                              | C <sub>LOAD</sub> = 10 nF, 80% to 20%                                                                                                                             | _    | 0.5  | _                    | μs   |

| Turn-On Pulse Current                                             | I <sub>GP</sub>                             |                                                                                                                                                                   | 8.5  | 10   | 12.5                 | mA   |

| Turn-On Pulse Time                                                | t <sub>GP</sub>                             |                                                                                                                                                                   | 22   | _    | 42                   | μs   |

| On Hold Current                                                   | I <sub>GH</sub>                             |                                                                                                                                                                   | _    | 400  | _                    | μΑ   |

| Dull Davis On Basistanas [2]                                      | Б                                           | $T_J = 25^{\circ}C, I_G = 10 \text{ mA}$                                                                                                                          | _    | 5    | _                    | Ω    |

| Pull-Down On Resistance [3]                                       | R <sub>DS(on)DN</sub>                       | $T_J = 150$ °C, $I_G = 10$ mA                                                                                                                                     | _    | 10   | _                    | Ω    |

|                                                                   |                                             | $V_{VIN} > 5.5 \text{ V (w.r.t. } V_{S}, \text{ or VIN if } V_{S} > V_{VIN})$                                                                                     | 8    | 9    | 12                   | V    |

| Gz and G <sub>VBB</sub> High Output Voltage                       | $V_{GH}$                                    | $4.5 \text{ V} < \text{V}_{\text{VIN}} \le 5.5 \text{ V} \text{ (w.r.t. V}_{\text{S}}, \text{ or VIN if V}_{\text{S}} > \text{V}_{\text{VIN}}$ ), Buck-Boost mode | 7.2  | 9    | _                    | V    |

| Gz and G <sub>VBB</sub> Low Output Voltage                        | $V_{GL}$                                    | –10 μA < I <sub>G</sub> < 10 μA                                                                                                                                   | _    | _    | V <sub>S</sub> + 0.3 | V    |

| Gz and G <sub>VBB</sub> Passive Pull-Down                         | R <sub>GPD</sub>                            | $V_{G} - V_{S} < 0.3 \text{ V}$                                                                                                                                   | _    | 950  | _                    | kΩ   |

| Gz and G <sub>VBB</sub> External Load Resistance [2]              | $R_{G}$                                     | Between gate and source (using ±1% resistor)                                                                                                                      | 100  | _    | _                    | kΩ   |

| GATE DRIVE DIAGNOSTICS AND F                                      | ILTERING (z :                               | = U, V, W)                                                                                                                                                        |      |      | ·                    |      |

| Gz and G <sub>VBB</sub> UV Threshold Rising                       | V <sub>G(UV,H)</sub>                        | V <sub>G</sub> rising (w.r.t. V <sub>S</sub> )                                                                                                                    | 6.0  | _    | 7.1                  | V    |

| Gz and G <sub>VBB</sub> UV Threshold Hysteresis [2]               | V <sub>G(UV,HYS)</sub>                      |                                                                                                                                                                   | _    | 250  | _                    | mV   |

| Gz and G <sub>VBB</sub> OV Threshold Falling                      | $V_{G(OV,L)}$                               | V <sub>G</sub> falling (w.r.t. V <sub>S</sub> )                                                                                                                   | 0.35 | _    | 1.05                 | V    |

| Gz and G <sub>VBB</sub> OV Threshold Hysteresis [2]               | V <sub>G(OV,HYS)</sub>                      |                                                                                                                                                                   | _    | 150  | _                    | mV   |