## **Automotive Stepper Driver**

### FEATURES AND BENEFITS

- Peak motor current up to 1.6 A at 28 V.

- Low  $R_{DS(ON)}$  outputs, 0.5  $\Omega$  source and sink typical

- Continuous operation at high ambient temperature

- 3.7 to 42 V supply operation

- Adaptive mixed current decay

- Synchronous rectification for low power dissipation

- Output slew control and PWM frequency spreading for EMC noise reduction

- Internal overvoltage and undervoltage lockout

- Hot warning and overtemperature shutdown

- Short-circuit, open-load diagnostics

- Programmable motion control

- Configurable through serial interface

- Simple step and direction control option

## **APPLICATIONS**

- Automotive stepper motors

- Engine management

- Headlamp positioning

- HVAC flap and valve control

### PACKAGE:

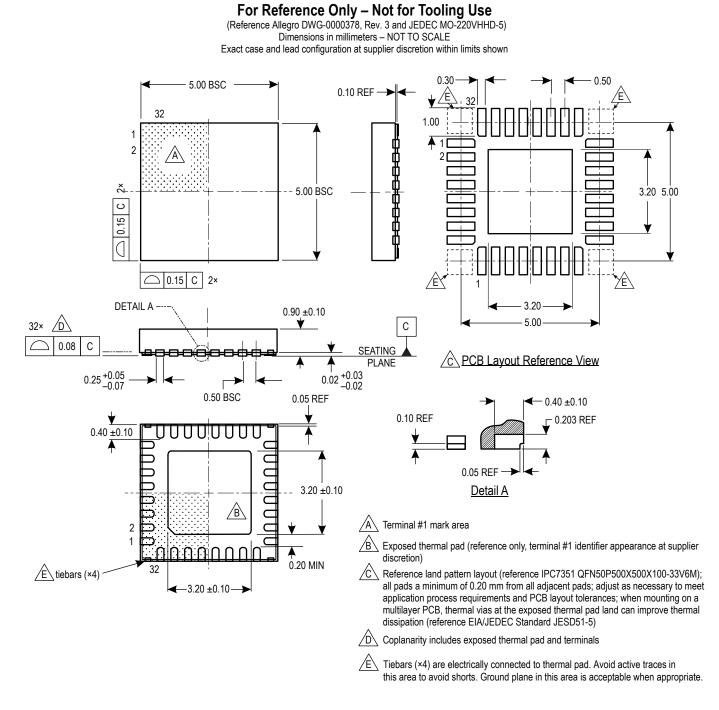

32-Pin QFN with Exposed Thermal Pad (suffix ET)

Not to scale

### DESCRIPTION

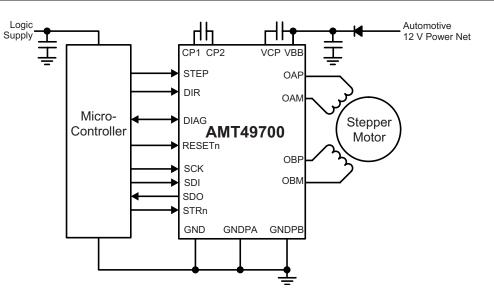

The AMT49700 is a flexible microstepping stepper motor driver with integrated phase current control, a built-in translator, and simple motion control. It is a single chip solution designed to operate bipolar stepper motors in full, half, quarter, eighth and sixteenth step modes, at up to 28 V.

The current regulator operates with fixed frequency PWM and uses adaptive mixed current decay to reduce audible motor noise and increase step accuracy. The current in each phase of the motor is controlled through a DMOS full-bridge using synchronous rectification to improve power dissipation. Internal circuits and timers prevent cross-conduction and shoot through when switching between high-side and low-side drives.

The outputs are protected from short circuits and features for low load current detection are included. Chip level protection includes hot thermal warning, overtemperature shutdown, overvoltage lockout, and undervoltage lockout.

The AMT49700 is fully controlled and configured through an SPI-compatible serial interface. It provides single step control with adjustable microstep resolution for fine positioning control and programmable motion control providing independent motor acceleration, deceleration, start speed, run speed, and number of steps with a single SPI command. In addition, detailed diagnostics are available on the serial data output.

The AMT49700 is supplied in a 32-terminal 5 mm  $\times$  5 mm QFN package with an exposed thermal pad (package type ET).

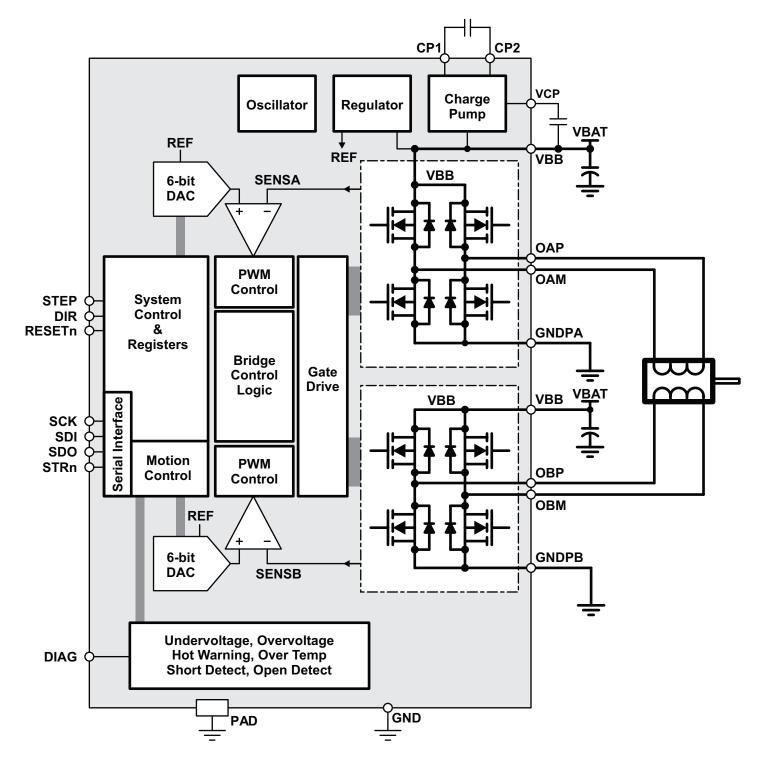

Figure 1: Typical Application Diagram

# **Automotive Stepper Driver**

#### **Selection Guide**

| Part Number Packing |                             | Package                                                            |

|---------------------|-----------------------------|--------------------------------------------------------------------|

| AMT49700KETJTR      | 1500 pieces per 7-inch reel | 5 mm × 5 mm, 0.9 mm nominal height<br>QFN with exposed thermal pad |

## **Table of Contents**

| Features and Benefits             |   |

|-----------------------------------|---|

| Description                       |   |

| Applications                      |   |

| Package                           |   |

| Typical Application Diagram       |   |

| Selection Guide                   |   |

| Specifications                    |   |

| Absolute Maximum Ratings          |   |

| Thermal Characteristics           |   |

| Pinout Diagram and Terminal List  |   |

| Functional Block Diagram          |   |

| Electrical Characteristics        |   |

| Timing Diagrams                   | 9 |

| Functional Description            |   |

| Terminal Functions                |   |

| Stepper Motor Motion Control      |   |

| Single-Step Control               |   |

| Step-Sequence Control             |   |

| Driving a Stepper Motor           |   |

| Phase Current Control             |   |

| Phase Current Table               |   |

| PWM Frequency                     |   |

| PWM Frequency Dither              |   |

| Low Power Sleep Mode              |   |

| Diagnostics                       |   |

| System Diagnostics                |   |

| Supply Voltage Monitors           |   |

| Temperature Monitors              |   |

| Bridge and Output Diagnostics     |   |

| Shorted Load                      |   |

| Overcurrent Fault Blanking        |   |

| Overcurrent Fault Reset and Retry |   |

| Open-Load Detection                       | 19 |

|-------------------------------------------|----|

| False State Reset                         | 20 |

| Reset Pulse                               | 20 |

| Reset Command                             | 20 |

| Sleep                                     | 20 |

| Diagnostic Register Read                  | 20 |

| Status Register Read                      | 20 |

| Stepping                                  |    |

| Disable Serial Reset                      | 20 |

| Step Angle Reset                          | 20 |

| Braking                                   |    |

| Serial Interface                          | 21 |

| Serial Registers Definitions table        | 21 |

| Serial Register Content                   | 23 |

| Status and Diagnostic Registers           |    |

| Resetting Status and Diagnostic Registers |    |

| Serial Register Reference                 |    |

| Phase Current Table                       | 32 |

| Applications Information                  | 33 |

| Motor Microstepping                       | 33 |

| Phase Table and Phase Diagram             |    |

| Microstepping with the Step Sequencer     | 35 |

| Single-Step Control                       | 37 |

| Motion Control with the Step Sequencer    | 39 |

| Profile Command Update                    | 41 |

| Continuous Run Mode                       | 41 |

| Layout                                    | 42 |

| Decoupling                                | 42 |

| Grounding                                 | 42 |

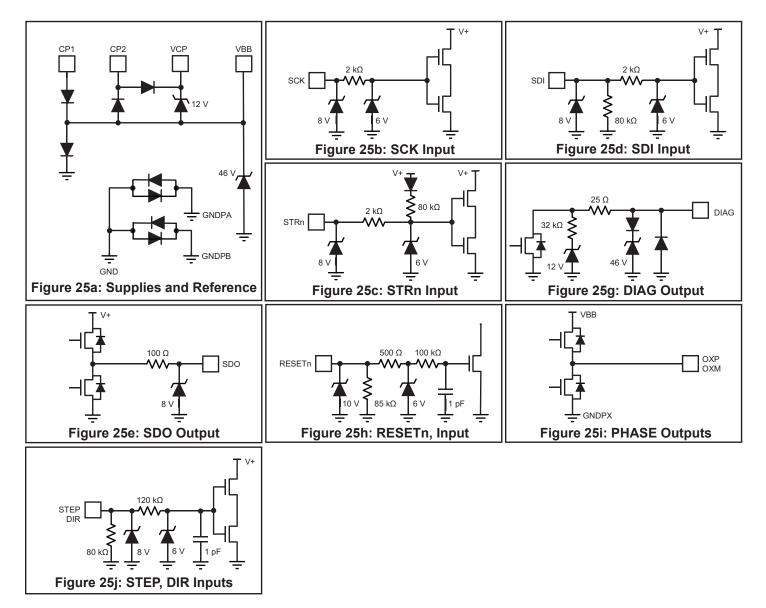

| Input/Output Structures                   | 43 |

| Package Outline Drawing                   | 44 |

|                                           |    |

# **Automotive Stepper Driver**

## **SPECIFICATIONS**

#### ABSOLUTE MAXIMUM RATINGS [1]

| Characteristic                                     | Symbol                                     | Notes                                                                                                                             | Rating                        | Unit |

|----------------------------------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|

| Load Supply Voltage                                | V <sub>BB</sub>                            |                                                                                                                                   | -0.3 to 42                    | V    |

| Terminal CP1                                       | V <sub>CP1</sub>                           |                                                                                                                                   | –0.3 to V <sub>BB</sub> + 0.3 | V    |

| Terminal CP2                                       | V <sub>CP2</sub>                           |                                                                                                                                   | –0.3 to V <sub>BB</sub> + 8   | V    |

| Terminal VCP                                       | V <sub>CP</sub>                            |                                                                                                                                   | –0.3 to V <sub>BB</sub> + 8   | V    |

| Terminals STEP, DIR, SCK, SDI, SDO, STRn           |                                            |                                                                                                                                   | –0.3 to 6                     | V    |

| Terminal RESETn                                    | V <sub>RESETn</sub>                        | Can be pulled to $V_{BB}$ with 33 $k\Omega$                                                                                       | -0.3 to 6                     | V    |

| Terminal DIAG                                      | V <sub>DIAG</sub>                          |                                                                                                                                   | -0.3 to 40                    | V    |

| Terminals OAP, OAM, OBP, OBM                       |                                            |                                                                                                                                   | –0.3 to V <sub>BB</sub>       | V    |

| Terminals GNDPA, GNDPB                             | V <sub>GNDPA</sub> ,<br>V <sub>GNDPA</sub> | All ground terminals must be connected together                                                                                   | -0.1 to 0.1                   | V    |

| Ambient Operating Temperature Range <sup>[2]</sup> | T <sub>A</sub>                             |                                                                                                                                   | -40 to 150                    | °C   |

| Maximum Continuous Junction Temperature            | T <sub>J(max)</sub>                        |                                                                                                                                   | 165                           | °C   |

| Transient Junction Temperature                     | T <sub>Jt</sub>                            | Overtemperature event not exceeding 10 seconds, lifetime duration not exceeding 10 hours, ensured by design and characterization. | 175                           | °C   |

| Storage Temperature Range                          | T <sub>stg</sub>                           |                                                                                                                                   | -55 to 150                    | °C   |

<sup>[1]</sup> With respect to GND

<sup>[2]</sup> Limited by power dissipation

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol                | Test Conditions <sup>[3]</sup>                                                          | Value | Unit |

|----------------------------|-----------------------|-----------------------------------------------------------------------------------------|-------|------|

| Package Thermal Resistance | $R_{	extsf{	heta}JA}$ | High-K PCB (multilayer with significant copper areas, based on JEDEC standard JESD51-7) | 30    | °C/W |

<sup>[3]</sup> Additional thermal information available on the Allegro website.

## **Automotive Stepper Driver**

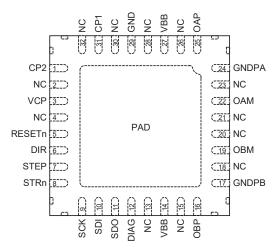

## PINOUT DIAGRAM AND TERMINAL LIST

#### **Terminal List Table**

| Number | Name   | Function                          |

|--------|--------|-----------------------------------|

| 31     | CP1    | Charge Pump Capacitor             |

| 1      | CP2    | Charge Pump Capacitor             |

| 12     | DIAG   | Diagnostic output                 |

| 6      | DIR    | Direction Input                   |

| 29     | GND    | Ground                            |

| 24     | GNDPA  | Power Ground for A Phase          |

| 17     | GNDPB  | Power Ground for B Phase          |

| 22     | OAM    | Bridge A negative output          |

| 25     | OAP    | Bridge A positive output          |

| 19     | OBM    | Bridge B negative output          |

| 16     | OBP    | Bridge B positive output          |

| 5      | RESETn | Standby Mode Control              |

| 9      | SCK    | Serial Clock Input                |

| 10     | SDI    | Serial Data Input                 |

| 11     | SDO    | Serial Data Output                |

| 7      | STEP   | Step Input                        |

| 8      | STRn   | Serial Strobe (chip select) Input |

| 27     | VBB    | Main Supply                       |

| 14     | VBB    | Main Supply                       |

| 3      | VCP    | Pump Storage Capacitor            |

| PAD    | -      | Exposed Thermal Pad               |

## **Automotive Stepper Driver**

FUNCTIONAL BLOCK DIAGRAM

# **Automotive Stepper Driver**

### ELECTRICAL CHARACTERISTICS: Valid at T<sub>J</sub> = -40°C to 150°C, V<sub>BB</sub> = 5.5 to 28 V, unless otherwise specified

| Characteristic                            | Symbol              | Test Conditions                                                                                                  | Min. | Тур. | Max.              | Units |

|-------------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------|------|------|-------------------|-------|

| SUPPLIES                                  |                     |                                                                                                                  |      |      |                   |       |

|                                           |                     | No unsafe states                                                                                                 | 0    | _    | 42                | V     |

| Supply Voltage Range [4][5]               | V <sub>BB</sub>     | Outputs driving                                                                                                  | 5.5  | -    | V <sub>BBOV</sub> | V     |

|                                           |                     | DIS = 1                                                                                                          | -    | -    | 25                | mA    |

| Supply Quiescent Current                  | I <sub>BBQ</sub>    | Sleep Mode, V <sub>BB</sub> = 12 V, GTS = 1,<br>STRn = 1 or V <sub>RESETn</sub> < 0.5 V, T <sub>J</sub> = 25°C   | -    | 20   | 40                | μA    |

|                                           |                     | Sleep Mode, V <sub>BB</sub> = 12 V, GTS = 1,<br>STRn = 1 or V <sub>RESETn</sub> < 0.5 V, T <sub>J</sub> = 150°C  | -    | 60   | 100               | μΑ    |

|                                           |                     | VLR = 0                                                                                                          | 3.1  | 3.3  | 3.5               | V     |

| Logic I/O Regulator Voltage               | V <sub>LIO</sub>    | VLR = 1                                                                                                          | 4.8  | 5.0  | 5.2               | V     |

| Charge Pump Voltage                       | V <sub>CP</sub>     | With respect to $V_{BB}$ , $V_{BB} > 7.5$ V, DIS = 1,<br>GTS = 0, RESETn = 1                                     | -    | 7.0  | _                 | V     |

| MOTOR BRIDGE OUTPUT                       |                     | ·                                                                                                                |      |      |                   |       |

| Link Oide On Desisters                    | R <sub>ONH</sub>    | $V_{BB} \ge 7 \text{ V}, \text{ I}_{OUT} = -1 \text{ A}^{[1]}, \text{ T}_{J} = 25^{\circ}\text{C}$               | _    | 500  | 600               | mΩ    |

| High-Side On-Resistance                   |                     | V <sub>BB</sub> = 13.5 V, I <sub>OUT</sub> = -1 A <sup>[1]</sup> , T <sub>J</sub> = 150°C                        | -    | 900  | 1100              | mΩ    |

| Llink Cide Dedu Diede Ferrured ) (elterne | V <sub>FH</sub>     | I <sub>F</sub> = 1 A                                                                                             | _    | -    | 1.4               | V     |

| High-Side Body Diode Forward Voltage      |                     | I <sub>F</sub> = 0.1 A                                                                                           | -    | -    | 1.2               | V     |

|                                           | R <sub>ONL</sub>    | V <sub>BB</sub> ≥ 7 V, I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 25°C,<br>MXI[4:0] = 331                          | -    | 500  | 600               | mΩ    |

| Low-Side On-Resistance                    |                     | V <sub>BB</sub> = 13.5 V, I <sub>OUT</sub> = 1 A, T <sub>J</sub> = 150°C,<br>MXI[4:0] = 331                      | _    | 900  | 1100              | mΩ    |

|                                           |                     | $V_{BB} \ge 7 \text{ V}, \text{ I}_{OUT} = 150 \text{ mA}, \text{ T}_{J} = 25^{\circ}\text{C},$<br>MXI[4:0] = 02 | _    | 1200 | 1800              | mΩ    |

|                                           |                     | V <sub>BB</sub> = 13.5 V, I <sub>OUT</sub> = 150 mA, T <sub>J</sub> = 150°C,<br>MXI[4:0] = 02                    | _    | 2100 | 3000              | mΩ    |

| Low Side Rody Diado Ferward Voltage       | V                   | $I_{\rm F} = -1  {\rm A}^{[1]}$                                                                                  | -    | -    | 1.4               | V     |

| Low-Side Body Diode Forward Voltage       | V <sub>FL</sub>     | $I_{\rm F} = -0.1  {\rm A}^{[1]}$                                                                                | -    | -    | 1.2               | V     |

|                                           |                     | GTS = 0, RESETn = 1, DIS = 1, $V_0 = V_{BB}$                                                                     | -    | 65   | 120               | μA    |

| Output Leakage Current <sup>[1]</sup>     |                     | GTS = 0, RESETn = 1, DIS = 1, V <sub>O</sub> = 0 V                                                               | -200 | -120 | -                 | μA    |

| Output Leakage Gullent 11                 | ILO                 | GTS = 1 or $V_{RESETn}$ < 0.5 V, $V_{O}$ = $V_{BB}$                                                              | -    | <1.0 | 20                | μA    |

|                                           |                     | GTS = 1 or $V_{RESETn}$ < 0.5 V, $V_O$ = 0 V                                                                     | -20  | <1.0 | _                 | μA    |

| Output Slew Rate                          | dV <sub>O</sub> /dt | SLEW = 0, V <sub>BB</sub> = 13.5 V                                                                               | -    | 100  | _                 | V/µs  |

|                                           |                     | SLEW = 1, V <sub>BB</sub> = 13.5 V                                                                               | -    | 30   | -                 | V/µs  |

Continued on the next page ...

# **Automotive Stepper Driver**

### ELECTRICAL CHARACTERISTICS (continued): Valid at T<sub>J</sub> = -40°C to 150°C, V<sub>BB</sub> = 5.5 to 28 V, unless otherwise specified

| Characteristic                          | Symbol             | Test Conditions                                    | Min.                                  | Тур.  | Max.                                  | Units |

|-----------------------------------------|--------------------|----------------------------------------------------|---------------------------------------|-------|---------------------------------------|-------|

| CURRENT CONTROL                         |                    | ·                                                  | · · · · · · · · · · · · · · · · · · · |       | · · · · · · · · · · · · · · · · · · · |       |

| System Clock Period                     | t <sub>osc</sub>   |                                                    | 47.5                                  | 50    | 52.5                                  | ns    |

| Dianity Times                           |                    | Default power-up value                             | 3.32                                  | 3.5   | 3.68                                  | μs    |

| Blank Time                              | t <sub>BLANK</sub> | Programmable range                                 | 1                                     | _     | 3.5                                   | μs    |

|                                         | £                  | Default power-up value                             | 18.32                                 | 19.20 | 20.24                                 | kHz   |

| PWM Frequency                           | f <sub>PWM</sub>   | Programmable range                                 | 16.4                                  | _     | 27.8                                  | kHz   |

| Debler DWAA Deebed                      |                    | Default power-up value, DS = 0                     | 49.4                                  | 52.0  | 54.6                                  | μs    |

| Bridge PWM Period                       | t <sub>PWM</sub>   | Programmable range, DS = 0                         | 36.0                                  | _     | 60.8                                  | μs    |

|                                         |                    | Default power-up value                             | _                                     | 32    | _                                     | μs    |

| Maximum PWM On Time                     | t <sub>PMX</sub>   | Programmable range                                 | disable                               | _     | 56                                    | μs    |

|                                         |                    | Default power-up value                             | -0.19                                 | -0.20 | -0.21                                 | μs    |

| Bridge PWM Dither Step Period           | ∆t <sub>PWM</sub>  | Programmable range                                 | -0.2                                  | _     | -1.6                                  | μs    |

|                                         |                    | Default power-up value                             | 0.95                                  | 1.00  | 1.05                                  | ms    |

| Bridge PWM Dither Dwell Time            | t <sub>DIT</sub>   | Programmable range                                 | 1                                     | _     | 10                                    | ms    |

|                                         | _                  | MXI[4:0] = 331                                     | _                                     | _     | ±10                                   | %     |

| Current Trip Point Error <sup>[2]</sup> | E <sub>ITrip</sub> | MXI[4:0] = 02                                      | _                                     | _     | ±15                                   | %     |

| LOGIC INPUT AND OUTPUT - DC             | PARAMETE           | RS                                                 | · · · ·                               |       |                                       |       |

| Input Low Voltage                       | V <sub>IL</sub>    |                                                    | _                                     | _     | 0.3 × V <sub>LIO</sub>                | V     |

| Input Low Voltage for Sleep Mode        | V <sub>ILS</sub>   | RESETn input only                                  | _                                     | _     | 0.5                                   | V     |

| Input High Voltage                      | VIH                |                                                    | $0.7 \times V_{LIO}$                  | _     | _                                     | V     |

| Input Hysteresis                        | V <sub>IHys</sub>  |                                                    | 100                                   | 300   | _                                     | mV    |

| Input Pull-Up Resistor                  | R <sub>PU</sub>    | STRn                                               | -                                     | 80    | _                                     | kΩ    |

| Input Pull-Down Resistor                | R <sub>PD</sub>    | SDI, STEP, DIR, RESETn                             | -                                     | 80    | _                                     | kΩ    |

| Output Low Voltage                      | V <sub>OL</sub>    | I <sub>OL</sub> = 1 mA                             | _                                     | _     | 0.4                                   | V     |

| Output High Voltage                     | V <sub>OH</sub>    | $I_{OL} = -1 \text{ mA}^{[1]}$                     | V <sub>LIO</sub> – 0.4                | _     | _                                     | V     |

| Output Leakage <sup>[1]</sup> (SDO)     | I <sub>OSD</sub>   | 0 V < V <sub>O</sub> < V <sub>LIO</sub> , STRn = 1 | -1                                    | _     | 1                                     | μA    |

| Output Leakage [1] (DIAG)               | I <sub>ODI</sub>   | 0 V < V <sub>0</sub> < 9 V                         | _                                     | _     | 1                                     | μA    |

| LOGIC INPUT AND OUTPUT - DY             | NAMIC PAR          | AMETERS <sup>[3]</sup>                             | · · · · · ·                           |       | ·                                     |       |

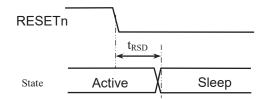

| Reset Pulse Width                       | t <sub>RST</sub>   |                                                    | 1.5                                   | _     | 8                                     | μs    |

| Reset Shutdown Pulse Width              | t <sub>RSD</sub>   |                                                    | 40                                    | -     | -                                     | μs    |

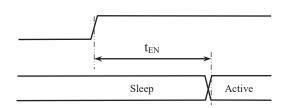

| Wake Up From Sleep                      | t <sub>EN</sub>    |                                                    | _                                     | -     | 1                                     | ms    |

| Interface Ready From Sleep              | t <sub>IR</sub>    |                                                    | _                                     | -     | 1.1                                   | ms    |

| Input Pulse Filter Time                 | t <sub>PIN</sub>   | STEP, DIR pin                                      |                                       | 1     | _                                     | μs    |

Continued on the next page ...

## **Automotive Stepper Driver**

### ELECTRICAL CHARACTERISTICS (continued): Valid at T<sub>J</sub> = -40°C to 150°C, V<sub>BB</sub> = 5.5 to 28 V, unless otherwise specified

| Characteristic                            | Symbol                | Test Conditions                | Min. | Тур.   | Max. | Units |

|-------------------------------------------|-----------------------|--------------------------------|------|--------|------|-------|

| SERIAL INTERFACE – DYNAMIC PA             | ARAMETER              | S <sup>[3]</sup>               | ,    |        |      |       |

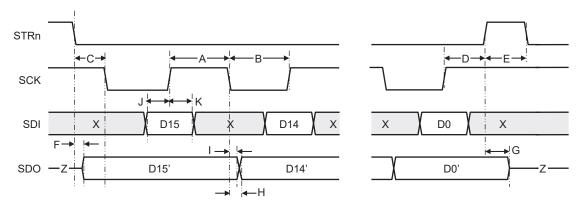

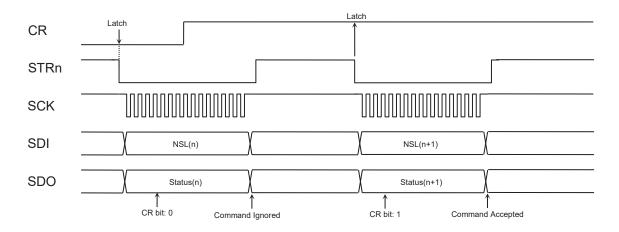

| Clock High Time                           | t <sub>scкн</sub>     | A[3]                           | 50   | _      | _    | ns    |

| Clock Low Time                            | t <sub>SCKL</sub>     | B [3]                          | 50   | _      | _    | ns    |

| Strobe Lead Time                          | t <sub>STLD</sub>     | C [3]                          | 150  | -      | _    | ns    |

| Strobe Lag Time                           | t <sub>STLG</sub>     | D [3]                          | 30   | -      | _    | ns    |

| Strobe High Time                          | t <sub>STRH</sub>     | E [3]                          | 350  | -      | _    | ns    |

| Data Out Enable Time                      | t <sub>SDOE</sub>     | F [3]                          | -    | -      | 40   | ns    |

| Data Out Disable Time                     | t <sub>SDOD</sub>     | G [3]                          | -    | -      | 30   | ns    |

| Data Out Valid Time from Clock Falling    | t <sub>SDOV</sub>     | H [3]                          | -    | -      | 45   | ns    |

| Data Out Hold Time from Clock Falling     | t <sub>SDOH</sub>     | [3]                            | 5    | -      | _    | ns    |

| Data In Setup Time to Clock Rising        | t <sub>SDIS</sub>     | J [3]                          | 15   | _      | _    | ns    |

| Data In Hold Time from Clock Rising       | t <sub>SDIH</sub>     | K <sup>[3]</sup>               | 10   | -      | _    | ns    |

| DIAGNOSTICS AND PROTECTION                | •                     |                                |      |        |      | -     |

| VBB Overvoltage Threshold [5]             | V <sub>BBOV</sub>     | V <sub>BB</sub> rising         | 32   | 34     | 36   | V     |

| VBB Overvoltage Hysteresis <sup>[5]</sup> | V <sub>BBOVHys</sub>  |                                | 2    | -      | 4    | V     |

| VBB Undervoltage Threshold <sup>[5]</sup> | V <sub>BBUV</sub>     | V <sub>BB</sub> falling        | 4.7  | 4.9    | 5.1  | V     |

| VBB Undervoltage Hysteresis               | V <sub>BBUVHys</sub>  |                                | 100  | 200    | 300  | mV    |

| VBB POR                                   | V <sub>BBPOR</sub>    | V <sub>BB</sub> falling        | -    | 3.2    | 3.7  | V     |

| VCP Undervoltage Threshold                | V <sub>CPUVH</sub>    | V <sub>CP</sub> falling        | 4.3  | 4.5    | 4.85 | V     |

| VCP Undervoltage Hysteresis               | V <sub>CPUVHHys</sub> |                                | 200  | 350    | 500  | mV    |

| High-Side Overcurrent Threshold           | I <sub>OCH</sub>      |                                | 1.6  | 2.2    | 3    | A     |

| High-Side Overcurrent Limit               | I <sub>LIMH</sub>     | Active during t <sub>OC</sub>  | 2.4  | 5.5    | 8    | A     |

| High-Side Overcurrent Margin              | I <sub>MAR</sub>      | $I_{MAR} = I_{LIMH} - I_{OCH}$ | 300  | -      | -    | mA    |

| Low-Side Overcurrent Threshold            |                       | MXI[4:0] = 331                 | 1.6  | 2.2    | 3    | A     |

| Low-Side Overcurrent Threshold            | I <sub>OCL</sub>      | MXI[4:0] = 02                  | 0.35 | 0.55   | 0.75 | A     |

| Overcurrent Fault Delay                   | t <sub>oc</sub>       | Default fault delay            | 1.9  | 2.0    | 2.1  | μs    |

| Open Load Current Threshold               | E                     | OLT = 0 (Default)              | 8    | 14     | 25   | mA    |

| Open Load Current Threshold               | E <sub>IOC</sub>      | OLT = 1                        | 21   | 28     | 39   | mA    |

| DIAG Output: Clock Division Ratio         | N <sub>D</sub>        |                                |      | 256000 |      |       |

| DIAG Output: Temperature Range            | V <sub>TJD</sub>      | DG[1:0] = 1,0                  | -    | 1440   | _    | mV    |

| DIAG Output: Temperature Slope            | A <sub>TJD</sub>      | DG[1:0] = 1,0                  | -    | -3.92  | _    | mV/°C |

| Hot Temperature Warning Threshold         | T <sub>JWH</sub>      | Temperature increasing         | 125  | 135    | 145  | °C    |

| Hot Temperature Warning Hysteresis        | T <sub>JWHHys</sub>   |                                | -    | 15     | _    | °C    |

| Overtemperature Shutdown                  | T <sub>JF</sub>       | Temperature increasing         | 170  | -      | 180  | °C    |

| Overtemperature Hysteresis                | T <sub>JHys</sub>     | Recovery = $T_{JF} - T_{JHys}$ | _    | 15     | _    | °C    |

[1] For input and output current specifications, negative current is defined as coming out of (sourcing) the specified device terminal.

[2] Gurrent Trip Point Error is the difference between actual current trip point and the target current trip point, referred to maximum full scale (100%) current:

Ē<sub>ITrip</sub> = 100 × (I<sub>TripActual</sub> − I<sub>TripTarget</sub>) / I<sub>FullScale</sub> %. <sup>[3]</sup> Timing parameter letters refer to Interface Timing Diagrams.

[4] Function is correct but parameters are not guaranteed above or below the general limits (5.5 to 28 V).

<sup>[5]</sup> Outputs disabled if  $V_{BB} > V_{BBOV}$  or  $V_{BB} < V_{BBUV}$  or  $V_{CP} < V_{CPUV}$ .

# **Automotive Stepper Driver**

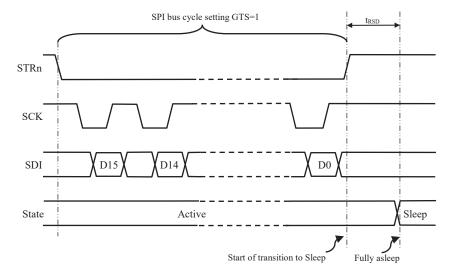

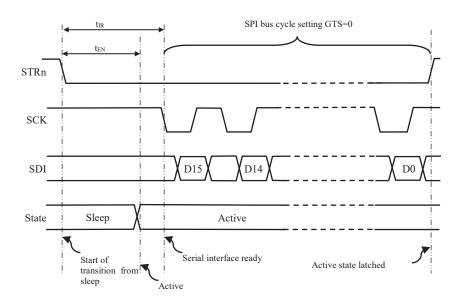

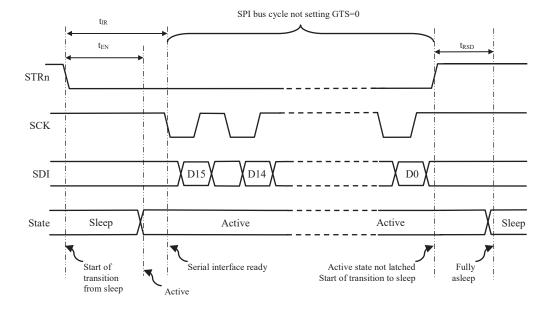

## TIMING DIAGRAMS

Figure 2: Serial Interface Timing (X = don't care; Z = high impedance (tri-state)

Figure 3a: Transition to Sleep (RESETn)

Figure 3b: Transition from Sleep (RESETn)

# **Automotive Stepper Driver**

Figure 4a: Transition to Sleep (SPI)

Figure 4b: Transition from Sleep (SPI, Active State Latched)

# **Automotive Stepper Driver**

Figure 4c: Transition from Sleep (SPI, Active State Not Latched)

## **Automotive Stepper Driver**

## FUNCTIONAL DESCRIPTION

The AMT49700 is an automotive stepper motor driver suitable for high temperature applications such as headlamp bending and leveling, throttle control, and gas recirculation control. It is also suitable for other low current stepper applications such as air conditioning and venting. It provides a flexible microstepping motor driver controlled through an SPI-compatible interface. The stepper motor can be controlled to provide single step movement, with adjustable microstep resolution for fine positioning control, or programmable multistep sequencing. The programmable step sequencer provides independent motor acceleration, deceleration, start speed, run speed, and number of steps with a single SPI command.

The SPI-compatible serial interface also allows the selection of step mode, configuration of motor control parameters, and programming of diagnostic thresholds.

A single diagnostic output provides simple indication of a fault condition and detailed diagnostic information can be read from the serial interface output.

The two DMOS full-bridges are capable of driving bipolar stepper motors in full-, half-, quarter-, eighth- and sixteenth-step modes, at up to 28 V, with phase current up to  $\pm 1.6$  A but limited by power dissipation and ambient temperature. For most applications, typical phase current is up to  $\pm 750$  mA. The current in each phase of the stepper motor is regulated by a fixed-frequency peak-detect PWM current control scheme operating in an adaptive mixed decay mode. This provides reduced audible motor noise and increased step accuracy for a wide range of motors and operating conditions.

The outputs are protected from short circuits and features for open load detection are included. Chip level protection includes hot thermal warning, overtemperature shutdown, and overvoltage and undervoltage lockout.

To assist with EMC compliance, the output slew rate is controlled at two programmable levels and the bridge PWM frequency includes optional programmable dither to spread the EM energy in the frequency spectrum.

## **Terminal Functions**

**VBB:** Main motor supply and chip supply for internal regulators and charge pump. Both VBB pins should be connected together and each decoupled to ground with a low ESR electrolytic capacitor and a good ceramic capacitor.

**CP1, CP2:** Pump capacitor connection for charge pump. Connect a 100 nF (50 V) ceramic capacitor, between CP1 and CP2.

**VCP:** Above supply voltage for high-side drive. A 100 nF (16 V) ceramic capacitor should be connected between VCP and VBB to provide the pump storage reservoir.

**GND:** Power and reference ground. Connect to GNDPA and GNDPB pins—see layout recommendations.

**GNDPA, GNDPB:** Bridge power grounds. Connect to GND—see layout recommendations.

**OAP, OAM:** Motor connection for phase A. Positive motor phase current direction is defined as flowing from OAP to OAM.

**OBP, OBM:** Motor connection for phase B. Positive motor phase current direction is defined as flowing from OBP to OBM.

SDI: Serial data input. 16-bit serial word, input MSB first.

**SDO:** Serial data output. High impedance when the STRn input is high. Outputs the FF bit of the Status register, the fault flag, as soon as the STRn input goes low.

**SCK:** Serial clock. Data is latched in from SDI on the rising edge of SCK. There must be 16 rising edges per write and SCK must be held high when the STRn input changes.

**STRn:** Serial data strobe and serial access enable. When STRn is high, any activity on SCK or SDI is ignored and SDO is high impedance, allowing multiple SDI slaves to have common SDI, SCK, and SDO connections.

**DIAG:** Diagnostic output. Function selected through serial interface. Default is fault output.

**RESETn:** Resets faults when pulsed low for a duration compliant with the Reset Pulse Width ( $t_{RST}$ ). Forces low-power shutdown (sleep) when held low for more than the Reset Shutdown Width ( $t_{RSD}$ ). Can be pulled to VBB with a 33 k $\Omega$  resistor.

**STEP:** STEP logic input. Motor advances on rising edge. Filtered input with hysteresis.

**DIR:** Direction logic input. Direction changes on next STEP rising edge. When high, the Phase Angle Number is increased on the rinsing edge of STEP. Has no effect when using the serial interface. Filtered input with Hysteresis.

## **Stepper Motor Motion Control**

The AMT49700 provides two methods of motion control, a single-step mode and a programmed step-sequence mode. Single-step mode can be controlled either by STEP and DIR terminals or through the serial interface. Step-sequence mode can only be controlled through the serial interface.

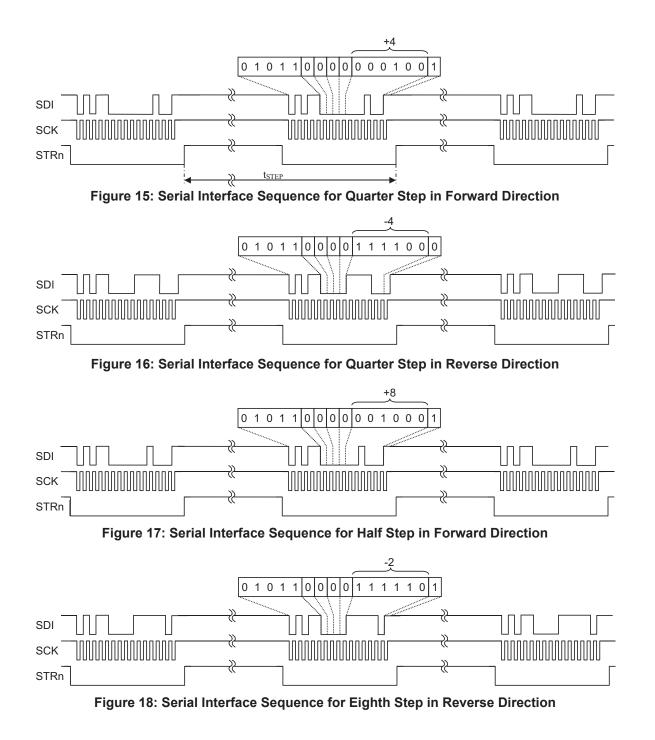

### SINGLE-STEP CONTROL

The single-step mode is accessed by writing a step change value into the SC[5:0] variable. The step change value is a two's complement (2'sC) number, where a positive value moves the motor forward by a number of 1/16th microsteps and a negative value moves the motor backwards by a number of 1/16th microsteps. For example, for a full-step forwards the decimal number 16 would be written to SC. For a half step backwards the number -8 would be written to SC. Further details and examples are provided in the applications section.

The Step and Direction control mode uses the STEP and DIR terminals. When using Step and Direction mode to control stepper motor, the AMT49700 automatically increases or decreases the Step Angle Number according to the step sequence associated with the selected step mode. The default step mode, reset at power-up or after a power-on reset, is half step. Full-, quarter-, and sixteenth-step sequences are also available when using the STEP and DIR inputs and are selected by the contents of MS[2:0].

### STEP-SEQUENCE CONTROL

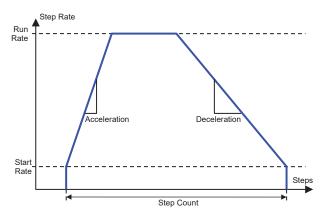

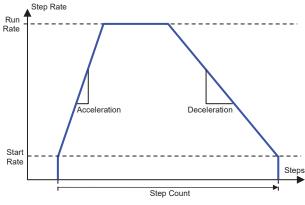

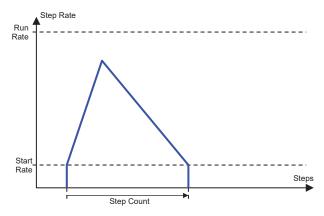

The step-sequence mode provides the ability to command the motor to run a number of steps in either direction following a programmable accelerate, run and decelerate profile. The acceleration, deceleration, running step rate, starting step rate, total number of steps and direction can all be configured independently through the serial interface by writing to the following variables:

| ACC[5:0]: | Acceleration in Full steps/s <sup>2</sup>  |

|-----------|--------------------------------------------|

| DEC[5:0]: | Deceleration in Full steps/s <sup>2</sup>  |

| SSR[5:0]  | Starting Step rate in Full steps/s         |

| RSR[5:0]  | Running Step rate in Full steps/s          |

| DIR       | Direction                                  |

| NSM[7:0]  | Most significant 8 bits of the step count  |

| NSL[7:0]  | Least significant 8 bits of the step count |

|           |                                            |

All step profile parameters are based on full step units except the

target steps, NSM[7:0] and NSL[7:0]. The actual motor speed, acceleration, deceleration and number of steps will always be the same regardless of the selected microstep resolution.

The sequence will start or change when STRn goes high at the end of the transfer of NSL[7:0], the least significant 8 bits of the step count number. When a programmed step sequence is complete, the motor will remain stopped until the end of the next NSL[7:0] transfer. When a programmed step sequence is in progress, the STEP and DIR inputs are ignored. The logic level on the DIR input has no effect on step-sequence control. In this operating mode, the direction is only defined by the DIR bit. Operational direction can be read on DIRR in Register 13 via serial interface either in the STEP and DIR mode or the Motion Control mode. The DIRR data is latched at the STRn signal taking low.

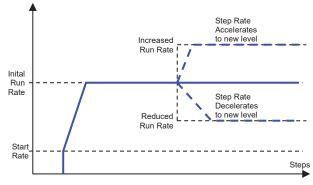

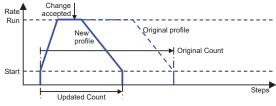

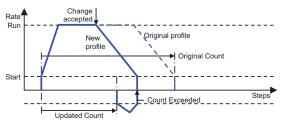

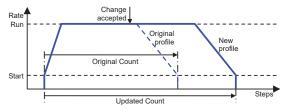

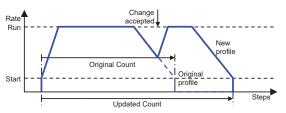

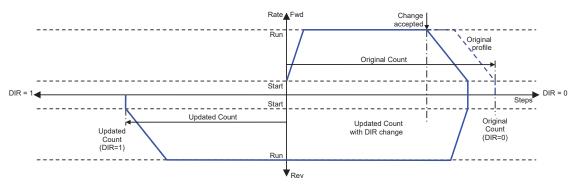

Figure 5 shows the definition of the basic step profile parameters and the sequence that occurs when the least significant 8 bits of the step count number are written. From a stationary state, the AMT49700 will begin by stepping the motor at the programmed start rate for the first step. The following steps will increase in step rate according to the programmed acceleration until the motor reaches the run step rate. At each step, the total step count remaining is reduced by one. The motor continues to be stepped at the run step rate until the step count reaches the number of steps required to decelerate the motor based on the run rate, the start rate and the deceleration factor. At this point the step rate is reduced at each step according to the programmed deceleration until the motor reaches the start step rate. Once the start step rate is achieved, the motor is stopped.

Figure 5: Step Profile Parameters

It is possible to change the variables when the step sequence is in progress, but the changes only take effect when the lsb of the step count is written. The effect of any change will depend on the present state of the step sequence. In each case, the AMT49700

will either continue running at the run step rate, accelerate the motor or decelerate the motor. However, note that changing the deceleration rate to zero, when the motor is running with a motion profile, will cause the motor to run continuously.

Three additional single bit commands, END, STP, and BRK, are available to bring the motor to a halt without having to change the step sequence variables. When set to 1, the END bit will immediately decelerate the motor to stop, based on the programmed deceleration value and the start run rate, regardless of the present speed. change in speed, or remaining step count. When set to 1, the STP bit will immediately cease any step sequence and stop and hold the motor. The BRK bit provides the additional ability to stop driving current into the motor and will short the windings to provide some amount of dynamic braking. Further details and examples are provided in the applications section. If a motion profile is initiated while either END or STP bits are set, the command is accepted and the CR bit is set low. The profile will not be imitated until the STP or END bits are set low.

## **Driving a Stepper Motor**

A two-phase stepper motor is made to rotate by sequencing the relative currents in each phase. In its simplest form, each phase is fully energized in turn by applying a voltage to the winding. For more precise control of the motor torque across temperature and voltage ranges, current control is required. For efficiency, this is usually accomplished using PWM techniques. In addition, current control also allows the relative current in each phase to be controlled, providing more precise control over the motor movement and hence improvements in torque ripple and mechanical noise.

For bipolar stepper motors, the current direction is significant, so the voltage applied to each phase must be reversible. This requires the use of a full-bridge (also known as an H-bridge), which can switch each phase connection to supply or ground.

## **Phase Current Control**

In the AMT49700, current to each phase of the two-phase bipolar stepper motor is controlled through a low-impedance n-channel DMOS full-bridge. This allows efficient and precise control of the phase current using fixed-frequency pulse-width-modulation (PWM) switching. The full-bridge configuration provides full control over the current direction during the PWM on-time and the current decay mode during the PWM off-time. The AMT49700 automatically controls the bridge decay mode to provide the optimum current control completely transparent to the user.

Each leg (high-side, low-side pair) of each bridge is protected from shoot-through by a fixed dead-time. This is the time

between switching off one MOSFET and switching on the complementary MOSFET. Cross-conduction is prevented by lockout logic in each driver pair.

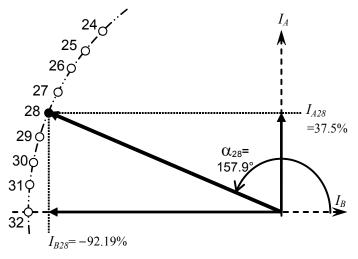

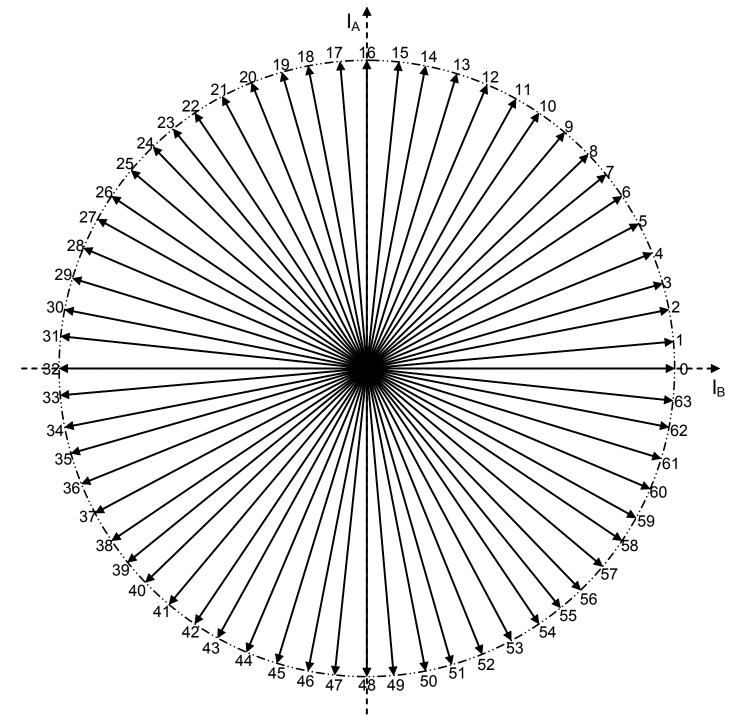

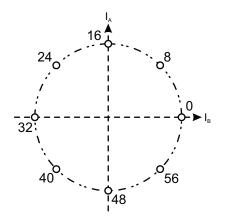

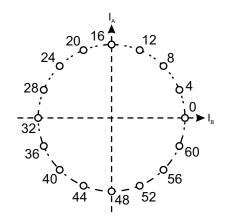

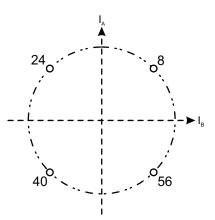

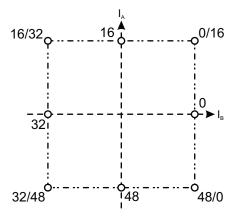

Except for the half-step uncompensated mode, the phase currents and, in particular, the relative phase currents are defined by the phase current table (Table 3). This table defines the two phase currents at each microstep position. For each of the two phases, the currents are measured in the bridge transistors on the AMT49700. The target current level is defined by the output from the digital-to-analog converter (DAC) for that phase.

The actual current delivered to each phase at each step angle is determined by the value of the MXI[4:0] variable and the contents of the phase table. For each phase, the value in the phase table is passed to the DAC, which uses MXI[4:0] as the reference 100% level (code 63) and reduces the current target depending on the DAC code. The output from the DAC is used as the input to the current comparators. The controlled step angle can be read out via serial interface, SA[5:0]. The SA value is equivalent to the Step number in sixteenth step (Table 3).

The one exception is the uncompensated half-step mode. In this mode, the current in each phase at the half-step positions (8, 24, 40, and 56), with both phases active, will be the same level as at the full-step detent positions (0, 16, 32, and 48), with one phase active.

Low-side on-resistance ( $R_{ONL}$ ) is automatically modified at maximum phase current settings of 120 mA or less (MXI[4:0] = 0...2) to maintain current-sense accuracy. High-side on-resistance ( $R_{ONH}$ ) remains constant across all maximum phase current settings.

The current comparison is ignored at the start of the PWM ontime for a duration referred to as the blank time. The blank time is necessary to prevent any capacitive switching currents from causing a peak current detection.

The PWM on-time starts at the beginning of each PWM period. The current rises in the phase winding until it reaches the required peak current level. At this point, the PWM off-time starts and the bridge is switched into fast decay. The current continues to be monitored. When the current drops below the peak current level, the bridge is switched into slow decay for the remainder of the PWM period. This mixed decay technique automatically adapts the current control to a wide range of motors and operating conditions in order to minimize motor torque ripple and motor noise. It also provides the lowest motor dissipation and highest motor efficiency over a wide range of voltage and temperature conditions.

The AMT49700 includes a programmable maximum PWM-on time limiter. In some cases, for example a phase short to ground, the motor current does not flow through the low side peak current sensor. In this case, the current measured by the peak current detector will not to reach the peak current threshold and the bridge would remain in the PWM-on state. This may allow the current to increase until it is limited only by the supply voltage and motor resistance. The maximum on time is set using the PM[4:0] variable as a maximum number of PWM periods from 1 to 56 in steps of 8 cycles. Setting PM[4:0] to 0 will disable the maximum PWM-on time limit. If the PWM-on time reaches the programmed limit the bridge will be disabled as if an overcurrent had been detected and an overcurrent will be indicated in the Diagnostic register for the high-side output of the opposite phase to the previously active phase. For example, if OAP is driven high and OAM driven low when the PWM-on time limit is reached then the AMH bit would be set indicating a possible short between OAM and GND and the bridge control follows the sequence as for an overcurrent detection.

## Phase Current Table

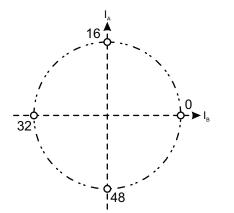

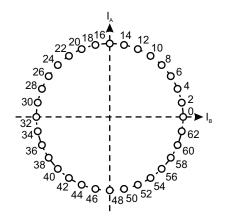

Except for the uncompensated half step mode, the relative phase currents are defined by the phase current table, Table 3. This table contains 64 lines and is addressed by the step angle number, where step angle 0 corresponds to  $0^{\circ}$  or  $360^{\circ}$ . The step angle number is generated internally by the step sequencer, which is controlled by the motion controller or by the step change value from the serial input. The step angle number determines the motor position within the  $360^{\circ}$  electrical cycle and a sequence of step angles determines the motor movement. Note that there are four full mechanical steps per  $360^{\circ}$  electrical cycle.

Each line of the phase current table has a 6-bit value, per phase, to set the DAC level for each phase plus an additional bit, per phase, to determine the current direction in each phase. The step angle number sets the electrical angle of the stepper motor in sixteenth microsteps, approximately equivalent to electrical steps of 5.625°.

On first power up, after a power-on reset or after sleep, the step angle number is set to 8, equivalent to the electrical 45° position, except for full-step single phase drive where the step angle number is set to 0. This position is defined as the "home" position.

When using the programmable step sequencer to control the stepper motor, the AMT49700 automatically increments or decrements the step angle according to the step angle sequence associated with the selected microstep mode. The default microstep mode is compensated half step. Full single-phase-, full two-phase-, uncompensated half-, quarter-, eighth- and sixteenth step sequences are also available when using the programmable step sequencer and are selected by the contents of the MS[2:0] variable.

When using single-step control option to control the stepper motor, a 6-bit step change value is written to SC[5:0] to increment or decrement the step angle. The step change value is a two's complement (2'sC) number, where a positive value increments the step angle and a negative value decrements the step angle. A single step change in the step angle is equivalent to a single 1/16th microstep. Therefore, for correct motor movement, the step change value should be restricted to no greater than 16 steps positive or negative.

This facility enables full control of the stepper motor at any microstep resolution up to 16th step, plus the ability to change microstep resolution "on-the-fly" from one microstep to the next. The only restriction is that the single-step control mode cannot operate in uncompensated half-step mode. The microstep mode selection set by MS[2:0] has no effect in single-step control.

In both control cases, the resulting step angle number is used to determine the phase current value and current direction for each phase based on the phase current table.

## **PWM Frequency**

The base frequency of the bridge PWM signal is fixed by the value of the base PWM period,  $t_{PW}$ . This base frequency can be altered by the frequency dither function described below.

The period of the PWM frequency is set by the PW[4:0] variable. The six bits of PW contain a positive integer that determines the PWM period derived by division from the system clock.

The PWM period is defined as:

$t_{\rm PW} = 36 \ \mu s + (n \times 0.8) \ \mu s$

where n is a positive integer defined by PW[4:0]

For example, when PW[4:0] = [1 0100], then  $t_{PW} = 52 \ \mu s$  and the PWM frequency is 19.2 kHz.

The range for the base PWM frequency is 16.4 kHz to 27.8 kHz. The accuracy of the PWM frequency is defined by the system clock accuracy.

## **Automotive Stepper Driver**

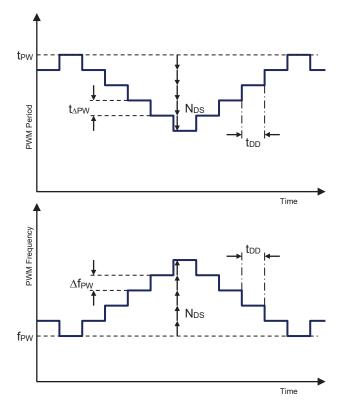

Figure 6: PWM Frequency Dither

### **PWM Frequency Dither**

The AMT49700 includes an optional PWM frequency dither scheme that can be used to reduce the peak radiated and conducted electromagnetic (EM) emissions. This is accomplished by stepping the PWM period in a triangular pattern in order to spread the EM energy created by the PWM switching. There are three programmable variables that can be used to adjust the frequency spreading for different applications. These are the dither step period,  $t_{\Delta PW}$ , dwell time,  $t_{DD}$ , and the number of steps in the pattern, N<sub>DS</sub>. These are identified in Figure 6.

Figure 6 shows the dithered period on top and the corresponding frequency below. The PWM frequency at any time is defined by the PWM period. The base PWM period,  $t_{PW}$ , is indicated as is the resulting base frequency,  $f_{PW}$ .

The dither step period,  $t_{\Delta PW}$ , is the incremental change in PWM period at each dither step and is defined by:

$$t_{\Delta PW} = -0.2 - (n \times 0.2) \ \mu s$$

where n is a positive integer defined by DP[2:0].

Following each change, the PWM period will remain at the new value for the duration of the dither dwell time, selected as 1 ms, 2 ms, 5 ms, or 10 ms by the contents of the DD[1:0] variable.

The number of dither steps,  $N_{DS}$ , is the value in the DS[3:0] variable. Starting at the base PWM period, the PWM period will decrease by the dither step period  $N_{DS}$  times then increase by the same amount and number of steps before restarting the cycle.  $N_{DS}$  can have a value between 0 and 15. A value of 0 will disable PWM frequency dither. The minimum PWM period in any case is 18 µs. If the frequency dither settings attempt to reduce the PWM period below 18 µs, then it will be held at 18 µs until the dther sequence brings the required value above 18 µs again.

As the frequency shift is defined by a fixed period change, the change in frequency will be slightly different for each step, but the frequency spreading effect will still be effective.

## Low-Power Sleep Mode

The AMT49700 can be put into a low power sleep mode by holding the RESETn input low for a duration of at least the Reset Shutdown Pulse Width,  $t_{RSD}$  (Figure 3a) or setting the GTS bit to 1 via the serial interface (Figure 4a). If GTS is used, the transition to sleep starts on the rising edge of STRn at the end of the serial write cycle and is completed one Reset Shutdown Pulse Width later. In combination, the two means of initiating sleep behave as detailed in Table 1.

| RESETn | GTS Bit | Mode   |

|--------|---------|--------|

| 0      | 0       | Sleep  |

| 0      | 1       | Sleep  |

| 1      | 0       | Normal |

| 1      | 1       | Sleep  |

#### Table 1: Sleep Mode Logic

In sleep mode, the outputs are disabled and the internal regulators are switched off to minimize current drain from the battery supply. If the initiation of sleep mode is successful, the DIAG output is set high; if unsuccessful, it is set low. This behavior occurs regardless of the value of the DGS[1:0] variable and may be used to confirm that a command to enter or exit sleep mode has been successful. The DIAG output state is not defined and should not be read during the Reset Shutdown Pulse Width,  $t_{RSD}$ , or Wake from sleep,  $t_{EN}$ , periods.

If sleep mode is initiated by taking RESETn low, it will be exited on the following rising edge on RESETn per Figure 3b. If sleep mode is initiated by setting GTS to 1, the part will start to wake up on the first falling edge on STRn as detailed in Figure 4b. The

serial transfer associated with the STRn falling transition initiating wake up must set GTS to 0, otherwise active mode will not be latched and the device will revert to sleep at the end of the cycle per Figure 4c.

Unlike other bus cycles, the first transfer after coming out of sleep mode must satisfy the constraint that the first falling edge on SCK does not occur until at least an Interface Ready period,  $t_{IR}$ , after the falling edge on STRn. This allows the internal regulators to power up and the interface logic to become active. During  $t_{IR}$ , any switching commands on STEP, DIR, STRn, SCK, and SDI should be avoided to avoid unpredictable operation.

If sleep mode is initiated by setting GTS to 1 and then RESETn is taken low, exit from sleep requires that RESETn is taken high prior to setting GTS to 0.

## Diagnostics

The AMT49700 integrates a number of diagnostic features to protect the driver and load as far as possible from fault conditions and extreme operating environments. When a fault condition is detected or confirmed then a fault state exists and the fault is captured by the diagnostic register and the status register. There are two types of fault conditions, defined as dynamic and static.

Dynamic fault conditions are those that only exist for a short duration, either due to some action being taken by the AMT49700 that removes the fault condition, or the fault is only detectable at specific instants. Fault states generated in response to Dynamic faults are latched to ensure that such faults are reported through the diagnostic output terminal, DIAG, and to ensure that dangerous conditions cannot return or persist to damage the AMT49700 or the load.

| Table | 2: | Fault | State | Table |

|-------|----|-------|-------|-------|

|-------|----|-------|-------|-------|

| Diagnostic             | Action          | Latched |

|------------------------|-----------------|---------|

| VBB Overvoltage        | Disable outputs | No      |

| VBB Undervoltage       | Disable outputs | No      |

| VCP Undervoltage       | Disable outputs | No      |

| Temperature Warning    | Flag fault only | No      |

| Overtemperature        | Disable outputs | No      |

| Bridge Short           | Disable output  | Yes     |

| Bridge Open            | Flag fault only | Yes     |

| Serial Interface Fault | Flag fault only | No      |

Bridge overcurrent (bridge short condition) and bridge open detect faults are categorized as Dynamic.

Static faults states are those that only exist when the fault condi-

tion is present. When such a fault condition is removed, the fault state is no longer present.

In both cases, the fault is always captured independently by the diagnostic or status registers. The contents of these registers are not reset when the fault state clears and provide a record of all faults that have occurred since the last reset of the register in question. Any fault bits set to 1 in the Diagnostic or Status registers are reset by a Status or Diagnostic register reset described below. If any static faults persist following a reset action the relevant fault states and register bits will reflect this immediately after completion of the reset.

A number of these features automatically disable the current drive to protect the outputs and the load. Others only provide an indication of the likely fault status. Fault states and associated actions are listed in Table 2.

A single open-drain diagnostic output (DIAG) can be programmed through the serial interface to provide four different fault signals.

At power-up or after a power-on-reset, the DIAG terminal outputs a general fault flag, which goes low when a fault state is present. It indicates that a static fault condition is present or a dynamic fault condition has been detected and latched.

In addition to the general fault flag, the DIAG output can be programmed via the serial interface to output any of seven other optional fault indicators:

- A supply voltage error signal, which is low when a VBB overvoltage, VBB undervoltage or VCP undervoltage fault state is present.

- An open load indicator.

- A voltage that represents the silicon temperature.

- A logic level version of the PWM switching on phase A.

- The internal step signal from the sequencer to the stepper driver.

- A step sequence activity indicator which is low when the SSA bit in the Status register is 1 and high when SSA is zero. This indicates when a programmed sequence of steps is actively running.

- A divided version of the internal system clock giving 78.125 Hz

The DIAG terminal will survive a maximum applied voltage of 40 V per the Absolute Maximum Ratings table, but switches into a high impedance state when the applied voltage exceeds approximately 16 V (regardless of programmed terminal function

or device status). On-state drive capability and off-state leakage current limits are defined in the Electrical Characteristics table by the  $V_{OL}$  and  $I_{ODI}$  parameters respectively and may be used to calculate a suitable pull-up resistance. In the majority of applications, a resistor in the range 10 k $\Omega$  to 20 k $\Omega$  is suitable.

## **System Diagnostics**

At the system level, the supply voltages and chip temperature are monitored.

## SUPPLY VOLTAGE MONITORS

The main supply VBB, the charge pump voltage VCP, and the internal supply voltages (derived from VBB but not externally accessible) are monitored—the main supply for overvoltage and undervoltage, the others for undervoltage only.

- If the main supply voltage,  $V_{BB}$ , rises above its overvoltage threshold,  $V_{BBOV}$ , the AMT49700 disables the outputs, drives the general fault flag (DIAG) low and sets the OV bit in the Status register to 1. When the main supply voltage falls below its overvoltage threshold,  $V_{BBOV}$   $V_{BBOVHys}$ , the outputs are re-enabled, the general fault flag goes high, and the OV bit remains set in the status register until cleared.

- If the main supply voltage,  $V_{BB}$ , falls below the VBB undervoltage threshold,  $V_{BBUV}$ , the AMT49700 disables the outputs, drives the general fault flag (DIAG) low, and sets the UV bit in the Status register to 1. If  $V_{BB}$  remains above the VBB POR threshold,  $V_{BBPOR}$ , but is low enough such that the I/O voltage is less than the programmed value, it is possible that the external microcontroller may not be able to communicate with the AMT49700 through the serial interface. However, in this case, all register states (including step angle) are retained. When  $V_{BB}$  rises above the undervoltage threshold,  $V_{BBUV} + V_{BBUVHys}$ , and no other faults are present, the outputs are re-enabled, the general fault flag goes high and the UV bit remains set in the status register until cleared.

- If the output of the charge pump,  $V_{CP}$ , falls below its undervoltage threshold,  $V_{CPUV}$ , the AMT49700 disables the outputs, drives the general fault flag (DIAG) low, and sets the UV bit in the Status register to 1. When the charge pump output rises above its threshold,  $V_{CPUV} + V_{CPUVHys}$ , and no other faults are present, the outputs are re-enabled, the general fault flag goes high, and the UV bit remains set in the status register until cleared.

- If  $V_{BB}$  falls below the VBB power-on reset (POR) level and the internal logic supply voltages derived from  $V_{BB}$  drop below acceptable levels, the AMT49700 is completely disabled. DIAG

is set low and held in this state for as long as the supply voltage permits. When the internal supply voltages rise to acceptable levels, a power-on reset takes place, the POR and FF bits are set to 1, and all other register bits are set to their default state. The VBB POR threshold,  $V_{BBPO}R$ , is an approximate value derived from the internal logic supply undervoltage threshold and the regulator dropout voltage. The AMT49700 is guaranteed not to be disabled if  $V_{BB}$  remains above the maximum value of  $V_{BBPOR}$ . The internal logic supply undervoltage threshold is set to guarantee that the internal logic will remain fully operational and correct down to the minimum value of the threshold.

If any of these supply fault states are present, and either the general fault flag or the supply fault flag is selected for output on DIAG, then DIAG will be low.

When applying power or when activating from sleep mode, the outputs should remain inactive for at least the wakeup from reset time,  $t_{EN}$ , to allow the internal charge pump and regulator to reach their full operating state.

The output drive MOSFETs of the AMT49700 remain protected from short circuits down to the VBB undervoltage level. However, when  $V_{BB}$  is less than 5.5 V, the overcurrent thresholds cannot be guaranteed to meet the precision specified at higher supply voltage. In addition, the open load detection may indicate a fault depending on the motor and load characteristics.

### **TEMPERATURE MONITORS**

Two temperature thresholds are provided: a hot warning and an overtemperature shutdown.

- If the chip temperature rises above the hot temperature warning threshold  $(T_{JW})$ , the hot warning bit (TW) is set to 1 in the Status register. No action is taken by the AMT49700. When the temperature drops below  $T_{JW}$  by more than the hysteresis value  $(T_{JWHys})$ , the fault state is cleared, but the TW bit remains at1 in the Status register until reset.

- If the chip temperature rises above the overtemperature threshold  $(T_{JF})$ , the overtemperature bit (OT) is set to 1 in the Status register, and the AMT49700 disables the outputs to try to prevent a further increase in the chip temperature. When the temperature drops below  $T_{JF}$  by more than the hysteresis value  $(T_{JFHys})$ , the fault state is cleared, and the outputs re-enabled. The OT bit remains at 1 in the Status register until reset.

If either of these supply fault states is present and the general fault flag is selected for output on DIAG, then DIAG will be low.

## **Bridge and Output Diagnostics**

The AMT49700 includes monitors that can detect a short to supply or a short to ground at the motor phase connections. These conditions are detected by monitoring the current from the motor phase connections through the bridge to the motor supply and to ground. In addition, a PWM-on time limiter is provided to ensure that any motor phase short to ground events do not cause the current to increase out of control indefinitely.

Low current comparators and timers are provided to help detect possible open load conditions.

### SHORTED LOAD

If the supply voltage is high enough to drive the bridge current above the overcurrent thresholds, a short across the load may be indicated by concurrent overcurrent fault states on both high-side and low-side MOSFETs.

### **OVERCURRENT FAULT BLANKING**

All overcurrent conditions are ignored for the duration of the overcurrent detection delay time ( $t_{OC}$ ) set between 1 and 4 µs by the contents of the TOC[1:0] variable. The overcurrent detection delay timer is started when an overcurrent condition is first detected. If the overcurrent condition is still present at the end of the overcurrent detection delay time, then an overcurrent fault state will be detected and latched. If the overcurrent condition is removed before the overcurrent detection delay time is complete, then the timer is reset and no fault is detected.

This prevents false overcurrent detection caused by supply and load transients. It also prevents false overcurrent detection from the current transients generated by the motor or wiring capacitance when a MOSFET is first switched on.

### OVERCURRENT FAULT RESET AND RETRY

Once an overcurrent fault state has been detected, all outputs for the phase where the fault state is present are disabled until the fault state is reset by a register reset. In addition, if the Overcurrent Fault Action bit, OFA, is set to 0, any overcurrent fault states are reset every time a step occurs either on a single step or on each step of a step sequence. When the fault state is reset the outputs are re-enabled and if the general fault flag is selected for output on DIAG and there are no other faults, then DIAG will be allowed to go high. The same sequence is also applied if the PWM-on time reaches the maximum limit.

Resetting overcurrent fault states every time a step occurs allows automatic restart when the cause of the overcurrent is removed.

If the cause of the overcurrent persists, the part will repeatedly cycle between overcurrent and attempted restart. In this condition, the device will not suffer damage, but if step demands are being applied at a high rate, the part may eventually shut down due to overtemperature.

If the OFA bit is set to 1, a step occurence does not reset overcurrent fault states and the automatic restart capability is disabled.

### **OPEN-LOAD DETECTION**

Open load detection is carried out on both phases and if either phase current drops below the open load current threshold,  $I_{OL}$ , an open-load state is flagged. ( $I_{OL}$  is set to either 13 mA or 26 mA, according to the state of the OLT bit.)

Unfortunately, simple current monitoring is only viable for stationary motors where the current rises quickly. When motors are running at high speed, phase current rise time is severely affected by motor back emf and the current may not reach its peak until late in the step period. Consequently, if open-load current comparisons were to run continuously, false open-load states would be flagged for at least part of the step period in many instances. To avoid such false states, the open-load comparator outputs are only checked after the expiry of the open-load detect time. This lockout period starts each time a step occurs and has a duration of 10 ms to 40 ms selected by the contents of the TOL[1:0] variable. Additionally, the comparator output for each phase is only checked if the target current for that phase is greater than twice the open load threshold current.

The AMT49700 continues to drive the bridge outputs under an open-load condition. Any open-load fault state is cleared when any of four events occurs:

- A single step command is received by writing to the single step command register with DSR = 0 or a rising signal at the STEP terminal.

- A step sequence is started by writing to the step count lsb register with DSR = 0.

- The phase current reaches the PWM threshold level.

- The open-load detect time expires and the phase current is detected to have risen above the open-load current threshold.

When an open-load fault is present and a rising edge is detected on the STEP input, this will both clear the fault and step the motor by the programmed microstep value. This will avoid any systematic step count misalignment if the open-load state is only temporary and the controller continues to step the motor without taking any action on the open-load detection.

## **False State Reset**

Various mechanisms may be used to reset or partially reset the AMT49700.

### **RESET PULSE**

Pulsing the RESETn input low for the duration of the reset pulsewidth time,  $t_{RST}$ , clears all dynamic fault states, the General Fault Flag (DIAG) and the Diagnostic and Status registers provided no static faults remain present.

### **RESET COMMAND**

Writing a 1 into the RST bit through the serial interface has the same effect as a pulse on the RESETn input. All dynamic fault states, the General Fault Flag (DIAG) and the Diagnostic and Status registers are cleared provided no static faults remain present.

### SLEEP

Entering and then exiting sleep mode (via RESETn) clears all fault states (with the exception of POR and FF) and the General Fault Flag (DIAG). If GTS bit is written with DSR = 1, the recorded faults will not be cleared. Additionally, the Diagnostic and Status registers (with the exception of POR and FF) are cleared.

### DIAGNOSTIC REGISTER READ

Reading the Diagnostic register via the serial interface, with DSR = 0, clears all overcurrent fault states and the overcurrent indicator bits in the Diagnostic register. Clearing all the overcurrent indicator bits will also clear the OCA and OCB bits in the Status register. Other bits in the Status register are not affected. Reading the Diagnostic register will have no effect on the state of the SSA bit. This is exclusively set or reset by the step sequence controller.

### STATUS REGISTER READ

Reading the Status register with DSR = 0 via the serial interface clears all latched fault states other than those generated by overcurrent faults. If no other faults are present this action also clears the General Fault Flag and the fault bits in the register except for the overcurrent bits, OCB and OCA, which are derived from the contents of the overcurrent indicator bits in the Diagnostic register. If any static faults are present, e.g. overtemperature, then the corresponding fault bit will not be affected by reading the Status register and will remain set.

### STEPPING

If the Overcurrent Fault Action bit, OFA, is set to 0 all overcurrent fault states and any associated fault indication on the General Fault

Flag are cleared on every time a step occurs either on a single step. This provides a means of automatically attempting a restart. No bits in the Diagnostic or Status registers are cleared thereby allowing suspected faults to be investigated via the serial interface.

If the OFA is set to 1, any overcurrent fault state will remain and automatic attempts continue stepping are disabled. Any step sequence in progress will stop immediately.

### DISABLE SERIAL RESET

The AMT49700 has a function to disable the fault reset action via the serial communication interface. When the DSR bit set to 1, AMT49700 will not clear the faults in Status and Diagnostics register by the reading command of Status and Diagnostics register. The CR and SSR are exclusively operated regardless of DSR. The reset command by RST bit or RESETn input pulse will operate as it is, even if DSR is set to 0.

## Step Angle Reset

The step angle number may be set to its home value by writing a logic 1 to the SAR bit in the Control register. If using the SAR bit, the step angle number reset only takes place on the rising edge on STRn at the end of the write cycle. Repeatedly overwriting the value 1 to the SAR bit repeatedly resets the step angle. The SAR bit may be cleared by writing 0 via the serial interface. The SAR bit is also reset to 0 by a power-on reset. Maintaining SAR at 1 does not lock the step angle in the home condition, and any step or sequence commands received via the serial interface are obeyed. The step angle reset action will not be taken if the following conditions are present: DIS, OT, OV, UV, BRK, and any short fault.

### Braking

The AMT49700 can be used to perform dynamic braking by setting the BRK bit to 1. If BRK is set to 1 and HLR = 0, all high-side MOSFETs are turned on and all low-side MOSFETs are turned off, effectively short-circuiting any back emf generated by the motor and creating a braking torque. If BRK is set to 1 and HLR = 1, all low-side MOSFETs are turned on and all high-side MOSFETs are turned off, producing a similar effect at the motor. During braking, motor current,  $I_{BREAK}$ , can be approximated by:

$$I_{\rm BRAKE} = V_{\rm BEMF} / R_{\rm L}$$

where  $V_{BEMF}$  is the voltage generated by the motor and  $R_L$  is the resistance of the phase winding. Care must be taken during braking to ensure that the power MOSFET maximum ratings are not exceeded. When dynamic braking is commanded, open-load conditions cannot be detected because of the bridge configuration that is enforced (both ends of each motor winding held in the same state).

# **Automotive Stepper Driver**

## SERIAL INTERFACE

#### **Serial Registers Definition\***

|                        | 15 | 14  | 13 | 12 | 11  | 10   | 9    | 8    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0   |

|------------------------|----|-----|----|----|-----|------|------|------|------|------|------|------|------|------|------|-----|

| 0: DWM Config          | 0  | 0   | 0  | 0  | WR  | PM4  | PM3  | PM2  | PM1  | PM0  | PW4  | PW3  | PW2  | PW1  | PW0  | Р   |

| 0: PWM Config          | 0  | 0   | 0  | 0  | WK  | 0    | 0    | 1    | 0    | 0    | 1    | 0    | 1    | 0    | 0    | Р   |

| 1: PWM Config          | 0  | 0   | 0  | 1  | WR  |      | DP2  | DP1  | DP0  | DD1  | DD0  | DS3  | DS2  | DS1  | DS0  | Р   |

| 1. FWM Coning          |    | 0   | 0  |    | WK  | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | Г   |

| 2: Current Config      | 0  | 0   | 1  | 0  | WR  | DIS  | HLR  | SLW  | TBK1 | TBK0 | MXI4 | MXI3 | MXI2 | MXI1 | MXI0 | Р   |

| 2. Guilent Conng       | 0  | 0   | -  |    |     | 1    | 0    | 0    | 1    | 1    | 1    | 0    | 0    | 0    | 0    |     |

| 3: Diagnostics Config  | 0  | 0   | 1  | 1  | WR  | DGS2 | DGS1 | DGS0 |      | OLT  | TOL1 | TOL0 | OFA  | TOC1 | TOC0 | Р   |

|                        |    |     |    | '  |     | 0    | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 1    |     |

| 5: Single Step Control | 0  | 1   | 0  | 1  | WR  | SAR  |      |      |      | SC5  | SC4  | SC3  | SC2  | SC1  | SC0  | Р   |

|                        | Ľ  |     |    |    |     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |     |

| 6: System Control      | 0  | 1   | 1  | 0  | WR  | GTS  | RST  | VLR  | MS2  | MS1  | MS0  | DSR  | BRK  | END  | STP  | Р   |

|                        |    |     |    |    |     | 0    | 0    | 0    | 0    | 1    | 0    | 0    | 0    | 0    | 0    | · · |

| 7: Step Count (Isb)    | 0  | 1   | 1  | 1  | WR  | DIR  | CRM  | NSL7 | NSL6 | NSL5 | NSL4 | NSL3 | NSL2 | NSL1 | NSL0 | Р   |

|                        |    |     |    |    |     | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    | · · |