使用 Allegro 电流传感器 IC(ACS724 和 ACS780)时实现共模场干扰最小化的技术

作者:Evan Shorman,

Allegro MicroSystems, LLC

简介

Allegro MicroSystems 电流传感器 IC 可以分为三大类:需要外部磁芯的传感器、具有封装内置磁芯的传感器,以及具有集成载流环(但无磁芯)的传感器。最后一类就是具有共模场抑制 (CMR) 功能的传感器。此应用注解将探讨 CMR 机制,并重点介绍如何充分利用此机制来优化电路板设计和布局。

背景

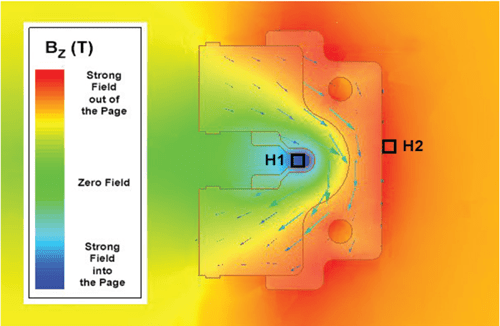

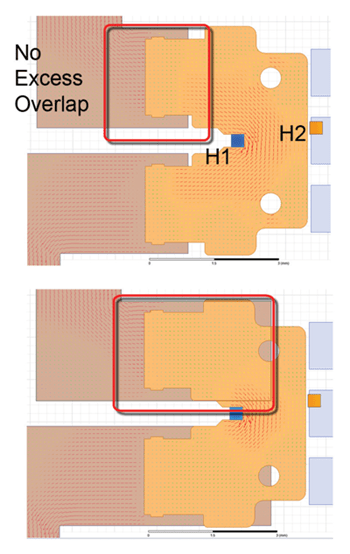

在使用集成载流环的 IC 中,载流环可以产生 IC 能测量的磁场。该磁场通过霍尔效应转换成电压。此霍尔电压正比于电流大小和方向。图 1 是特定电流传感器 IC 引线框产生磁场的示例。在该图中,箭头指示通过引线框的电流,色图描述了 100 A 直流电通过传感器时产生的磁场。为了表达清晰,图中移除了电流源。

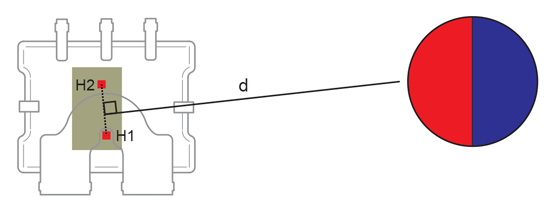

使用配备集成载流环的 IC 具有很多优势:无需磁芯、基本没有磁滞、功率低、并且具有较高的温度精确度。但是,由于不存在磁芯,传感器容易受到磁体或传感器 IC 周围导线电流产生的杂散磁场的影响。为了抑制杂散磁场的出现,Allegro 的很多电流传感器都具有双霍尔共模抑制方案。霍尔板的布置方式要确保当电流通过 IC 集成导体或载流环时,每个霍尔板感应的场极性相反。在图 1 中,两个霍尔板的位置用 H1 和 H2 表示。可以从图中看出,这两个区域具有方向相反的磁场。

这是所用 CMR 技术的基本原理:如果两个霍尔板的信号相减,然后可以将集成环引发的信号求和,这样就可以抑制来自入射 IC 的任何杂散磁场的共模(单极)信号。简单举例,假定每个霍尔板的磁场 ±B 大小相等,方向相反,则:

H1 – H2 ∝ B1 – B2

B – B2 = B – (–B)

B – (–B) = 2 × B

因此,

H1 – H2 ∝ 2 × B

假定两个霍尔板上具有相等的杂散磁场 Bext,则:

H1 – H2 ∝ B1 – B2

B1 – B2 = (B + Bext ) – (–B + Bext)

(B + Bext ) – (–B + Bext ) = 2 × B + Bext – Bext

2 × B + Bext – Bext = 2 × B

因此,

H1 – H2 ∝ 2 × B

应用注解无磁芯霍尔效应电流传感器 IC 采用的共模场抑制技术更详细地介绍了 CMR 技术的理论和指导方程。此应用注解涵盖的主要技术是如何设计和布置这些电流传感器 IC 的载流轨迹。此外,该应用注解提供了最小化其他杂散来源的指南。

临近电流产生的磁场

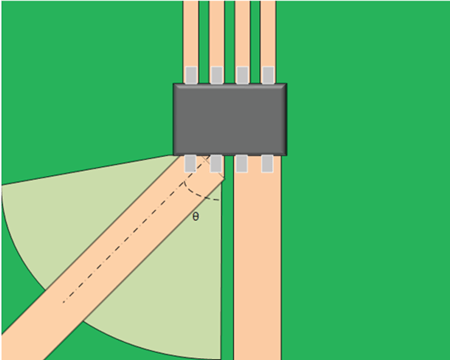

为了充分利用这些器件的 CMR 功能,包含 IC 的电路板应设计为两个霍尔板的外部磁场相同。这有助于最大限度减少载流 PCB 自身产生的外部磁场导致的错误。每个载流轨迹的三个主要参数据决定了导致 IC 错误:与 IC 的 距离、载流体的宽度以及它和 IC 之间的角度。图 2 是 IC 附近载流体布线的示例。器件和导体之间的距离 d 是器件中心与导体中心的距离。电流路径宽度是 w。器件和电流路径之间的角度 θ 是指连接两个霍尔板的直线与电流路径垂直线的夹角。

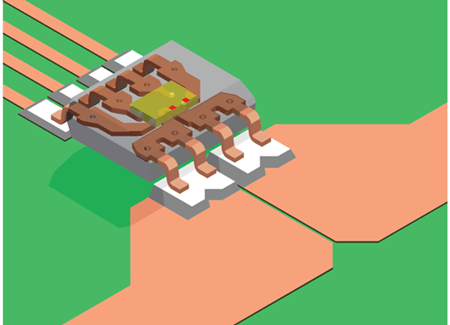

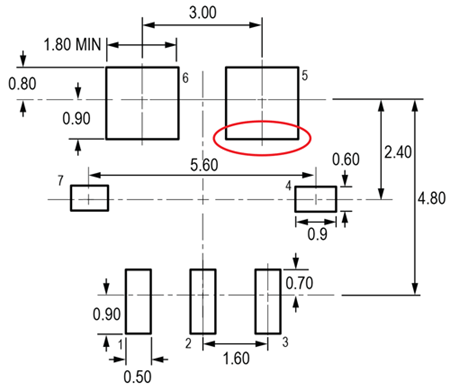

两个霍尔板的位置和方向随 IC 的不同而有所变化。例如,如图 3 所示,ACS724 的霍尔板相比 ACS 780 霍尔板旋转了 90°。如果在任何具有 CMR 功能的 Allegro、电流传感器 IC 附近进行电流路径布线,最好保持 θ 尽可能接近 90°。

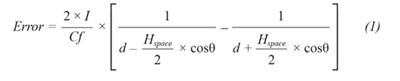

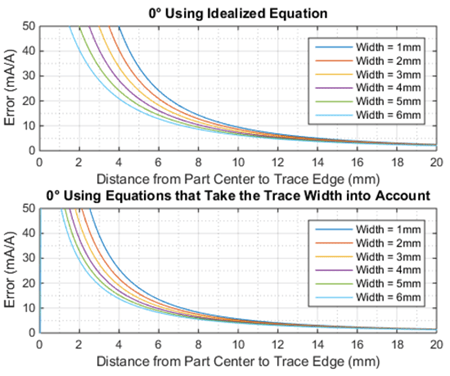

如果无法保持 θ 接近 90°,下一个最好的选择是保持电流路径与电流传感器 IC 之间距离 d 尽可能大。假定电流路径与 IC 的夹角最差,即 θ = 0° 或 180°,方程:

此处,H距离 是两个霍尔板之间的距离, Cf 是 IC 耦合因数。此耦合因数随 IC 不同而变化。ACS780 的耦合因数是 5 至 5.5 G/A,而其他 Allegro IC 的耦合因数范围是 10 至 15 G/A。

误差估计

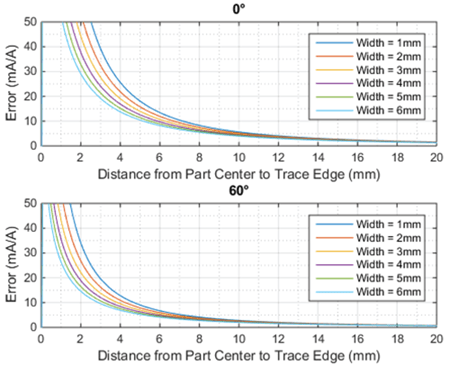

等式 1 假定是无限长、无限细的导线。它没有考虑载流导体的宽度和厚度。图 4 是在最差条件方向(θ = 0° 或 180°)计算得出的通过 ACS780 的载流体误差。该误差是采用理想等式以及考虑导体宽度和厚度的计算密集方程组计算得出。该图显示,计算误差高于使用理想方程的结果。因此,方程 1 可用于快速、保守估计误差。

使用更精确的计算法可以为不同宽度的电流路径以及器件和电流路径之间不同的角度计算误差。对于所有角度和宽度,假定使用 4 盎司规格铜导体设定电流轨迹厚度。该图表明,载流体宽度对误差有影响,但最大的影响因素是与器件的角度 θ 以及与器件的距离 d。

其他需要考虑的布局原则

如果布置包含具有 CMR 的 Allegro 电流传感器 IC 的电路板,所有载流路径的方向和接近性是重要因素,但优化 IC 性能还要考虑其他因素。可能影响系统误差的其他杂散场来源包括与 IC 集成载流体相连的轨迹以及临近永久磁体的位置。

必须小心规划电路板与电流传感器 IC 的连接方式。可能影响性能的常见错误是:

- 电流路径到 IP 管脚的接近角度

- 电流轨迹在 IC 下面扩展得过远

接近角度

使用 Allegro 电流传感器 IC 的一个常见错误是使用不良的电流引入角度。图 6 是电流轨迹接近 IC 的示例(此处是 ACS724)。此图显示 IP+ 和 IP– 的轨迹。浅绿色区是进入 IP+ 的理想接近区。该区域范围是 0° 至 85°。该规则同样适用于 IP– 轨迹。

该区域的限制是为了防止载流轨迹影响到可能导致 IC 输出误差的任何杂散场。如果与 IP 相连的电流轨迹在该区域外部,则必须按上述方式处理(临近电流路径导致的磁场)。

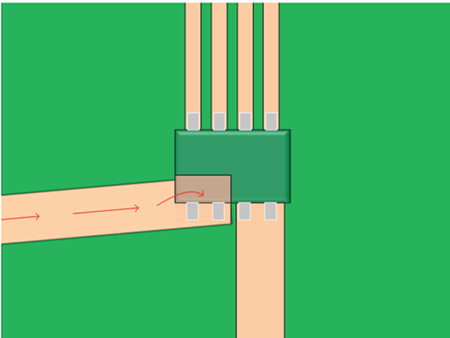

在IC 下面扩展

另一个常见错误是电流轨迹与 IP 管脚距离过远。根据器件的不同,这可能导致两种不同的问题。如果是采用 SOIC 和类似封装的器件,这可能导致 IC 上产生杂散场,使性能降低。如果采用 LR 封装,由于 IP 总线较大并且暴露在外,在封装下面过远布线可能改变通过 IP 总线的电流路径,从而改变器件的性能。下面章节将更详细地介绍对 LR 封装的影响。

对于杂散场而言,如果电流轨迹以一定的角度进入 IP 总线,问题会更加严重。如果发生这种情况,电流实际在部件下面流过,背向 IP 管脚,然后向上通过 IP 管脚。改变的电流路径可能会导致杂散场产生,降低 IC 精度。禁止在器件下面扩展至 IP 管脚的电流轨迹就可以防止这种情况。

永磁体影响

如果永久磁铁靠近电流传感器 IC,磁铁导致的杂散场也会影响 IC 性能。一般情况下,来自磁铁的杂散场可能随磁体的不同而变化极大。它取决于磁铁尺寸、材料、磁化方向以及其他很多因素。如果可以调整电流传感器,使霍尔板垂直于磁体(如图 8 所示),则可以将这些杂散场的影响降至最小。

LR 封装特定布局规则

在IC 下面扩展

在 LR 封装中,载流轨迹在器件下面扩展实际改变了电流通过 IP 总线的路径。这可能导致 IP 总线与 IC 的耦合因数发生变化,并显著降低器件性能。

使用 ANSYS Maxwell 电磁套件可以模拟电流密度和电流产生的磁场。图 9 提供两种不同模拟的结果。第一种情况是向上引至 IP 总线的电流轨迹在所需点终止。第二情况是电流轨迹向 IP 总线上方扩展过远。两个模拟中的红色箭头表示高电流密度的区域。在没有过量重叠的模拟中(红色区域),电流密度与具有过量重叠的模拟差距巨大。还可以看出,H1 场比没有过多重叠时更大。这一点用蓝色暗影表示。

重叠的 ACS780 引线框模拟

如果重叠超过推荐量,也会导致其他问题,例如电流接近角范围显著缩小。如果电流轨迹在 IP 总线上扩展的过大,则会形成对接近角的依赖,即接近角直接影响器件的耦合因数。避免这种情况的最佳方式是限制电流轨迹的重叠。

结论

Allegro MicroSystems 电流传感器 IC 有很多优势。这些传感器 IC 的磁滞几乎为零,而且功耗非常低。与缺少磁芯相伴的一个缺点是容易受到杂散磁场的影响。但是,很多 IC 可以抑制共模磁场。

两个霍尔板的共模场相等时,CMR 技术效果最好。我们探讨了若干显著降低两个霍尔板共模场差值的技术,即如何进行外部电流路径布线与其他优化布局技术。针对电流路径不能以最有利的方向布线的情况,我们还介绍了误差估算。我们还探讨了一些针对 LR 封装的布局技术,这是因为必须考虑 LR 的一些特性才能获得最优性能。

总之,本文探讨的技术和计算有助于客户优化 Allegro、电流传感器 IC 性能。