Have Questions? Let us help!

We're passionate about innovation. Reach out and you'll hear back from an expert shortly.

One of our solution experts will be in touch with you shortly. Keep reading to learn more about our industry leading solutions.

|

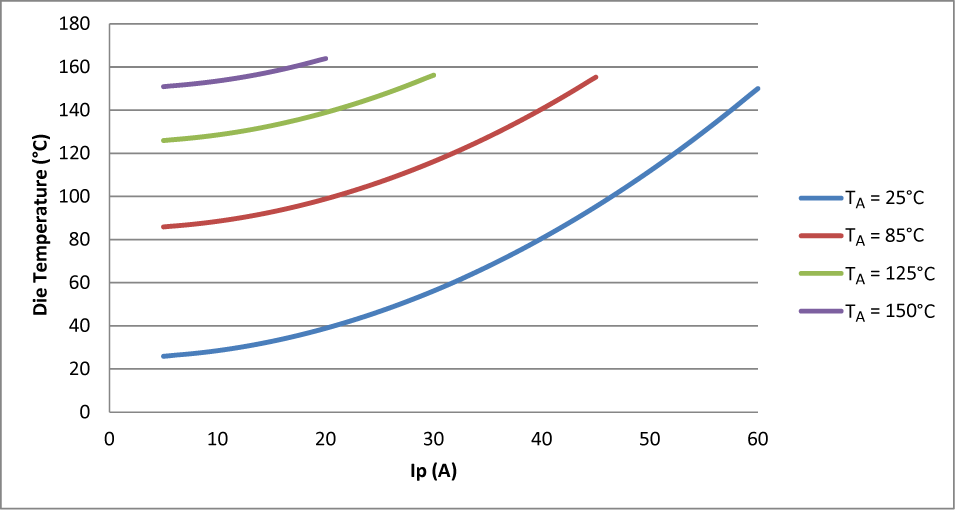

Table 4. Continuous Current Overcurrent Limits |

|

|

tA |

IP(OClim) |

|

25 |

50 |

|

85 |

40 |

|

125 |

25 |

|

150 |

20 |

|

Table 6. Typical Capacitive Coupling of |

||

|

Frequency |

VOUT |

Noise Rejection |

|

5 |

5 |

−72 |

|

10 |

16 |

−62 |

|

15 |

40 |

−54 |

|

20 |

58 |

−51 |